# Module-1 BJT AC Analysis:

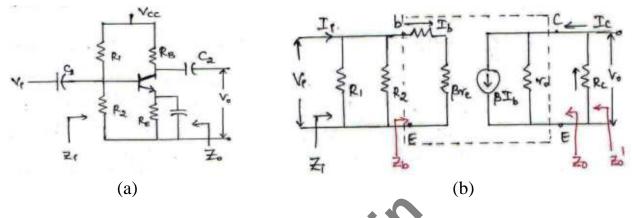

**BJT AC Analysis: BJT AC Analysis:** BJT Transistor Modeling, The re transistor model, Common emitter fixed bias, Voltage divider bias, Emitter follower configuration. Darlington connection-DC bias; The Hybrid equivalent model, Approximate Hybrid Equivalent Circuit-Fixed bias, Voltage divider, Emitter follower configuration; Complete Hybrid equivalent model, Hybrid  $\pi$  Model.

# **BJT Transistor Modeling**

- A model is an equivalent circuit that represents the AC characteristics of the transistor.

- Transistor small signal amplifiers can be considered linear for most application.

- A model is the best approximate of the actual behavior of a semiconductor device under specific operating conditions, including circuit elements

### **Transistor Models**

- $\checkmark$  r<sub>e</sub>- model any region of operation, fails to account for output impedance, less accuracy

- ✓ Hybrid model limited to a particular operating conditions, more accuracy

# The re Transistor Model

BJTs are basically current-controlled devices; therefore the  $r_e$  models uses a diode and a current source to duplicate the behavior of the transistor. One disadvantage to this model is its sensitivity to the DC level. This model is designed for specific circuit conditions.

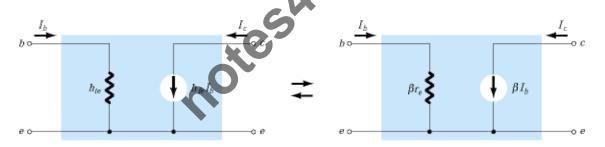

# **Common-Base Configuration**

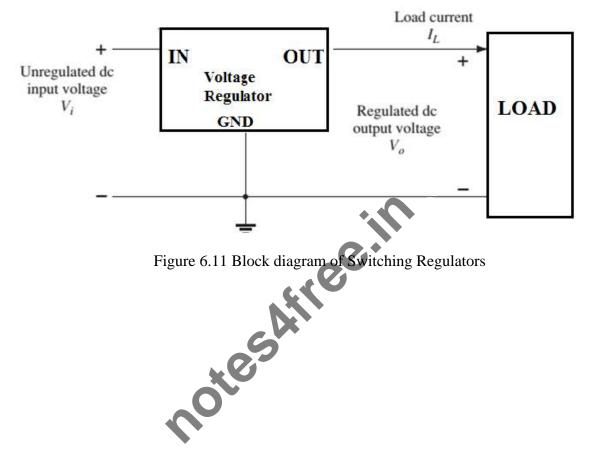

Figure 1 Common Base transistor re mode

We know that from diode equation  $r_e$  is defined as follows

$$I_{e} = \alpha I_{e}$$

$$r_{e} = \frac{26 \,\mathrm{mV}}{I_{e}}$$

Applying KVL to input and out circuit of figure 1(d), we will get

input impedance:  $Z_i = r_e$ **Output impedance:**  $Z_o = \infty$ **Voltage gain:**  $A_v = \frac{\alpha R_L}{r_e} = \frac{R_L}{r_e}$ sAtree ir **Current gain:**  $A_i = -\alpha = -1$ **Common-Emitter Configuration** B Ye (a) (b) 6 E (d) (c)

Figure 2 Common Emitter re model of npn transistor

3

Figure 1 (a) shows simple transistor circuit. Figure 1(b) and 1(c) shows evaluation transistor re model in CE configuration.

Applying KVL to input and out circuit of figure 2(d), we will get

input impedance:  $z_i = \frac{V_i}{I_i}$  $V_i = V_{be} = I_e r_e = \beta I_i r_e$

$$Z_i = r_e$$

$A_i = \beta$

**Output impedance:**  $Z_o = \infty$

Voltage gain:

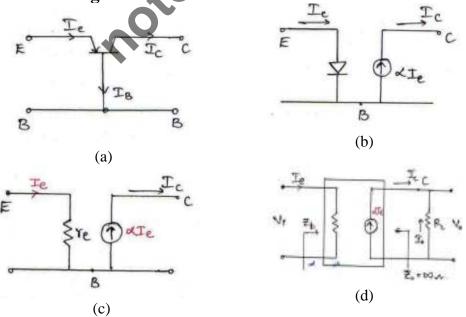

### **Fixed bias Common-Emitter Configuration**

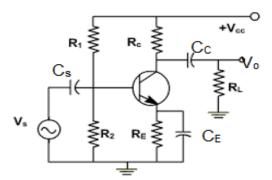

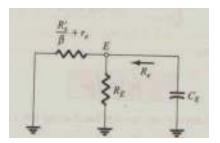

Figure 3 Fixed bias Common-Emitter Configuration

Note in Fig. 3 (a) that the common ground of the dc supply and the transistor emitter terminal permits the relocation of RB and Rc in parallel with the input and output sections of the transistor, respectively. In addition, note the placement of the important network parameters Zi, Zo, Ii, and Lo on the redrawn network. Substituting the remodel for the common-emitter configuration of Fig. 3(a) will result in the network of Fig. 3(b). Afree

#### • From the above r<sub>e</sub> model, **Input impedance**

$Z_i = [R_B || \beta r_e]$  ohms

If  $R_B > 10 \beta r_e$ , then,

$[\mathbf{R}_{\mathbf{B}} | | \beta \mathbf{r}_{\mathbf{e}}] \cong \beta \mathbf{r}_{\mathbf{e}}$

Then,  $Z_i \cong \beta r_e$

### **Output impedance**

$Z_0$  is the output impedance when  $V_i = 0$ . When  $V_i = 0$ , ib = 0, resulting in open circuit equivalence for the current source.

$Z_0 = [R_C || r_0]$  ohms

### Voltage gain

$V_o = -\beta I_b(R_c || r_o)$

- From the remodel,  $I_b = V_i / \beta r_e$

- thus,

$-V_0 = -\beta (V_i / \beta r_e) (R_C \parallel r_0)$

- $-Av = V_o / V_i = (Rc || r_o) / r_e$

- 10

- If  $r_0 > 10Rc$ ,

$$-Av = -(Rc/r_e)$$

• The negative sign in the gain expression indicates that there exists 1800 phase shift between the input and output.

### **Current gain:**

$$\begin{aligned} \mathbf{A}_{i} &= \frac{\mathbf{I}_{o}}{\mathbf{I}_{i}} = \frac{\beta \mathbf{R}_{B} \mathbf{f}_{o}}{(\mathbf{f}_{o} + \mathbf{R}_{C})(\mathbf{R}_{B} + \beta \mathbf{f}_{o})} \\ \mathbf{A}_{i} &\cong \beta \Big|_{\mathbf{f}_{o} \ge 10 \mathbf{R}_{C}, \mathbf{R}_{B} \ge 10, \mathbf{f}_{o}} \end{aligned}$$

$$A_i = -A_v \frac{Z_i}{R_c}$$

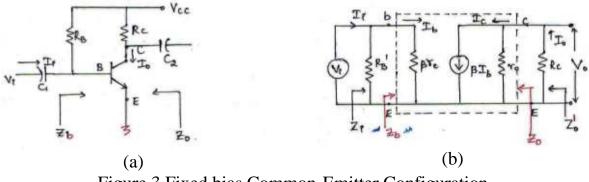

# **Common-Emitter Voltage-Divider Bias**

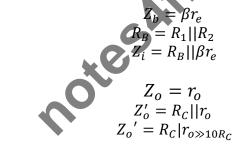

Figure 4 Voltage Divider bias Common-Emitter Configuration

The  $r_e$  model is very similar to the fixed bias circuit except for  $R_B$  is  $R_1 || R_2$  in the case of voltage divider bias.

Input impedance:

**Output impedance:**

**Voltage gain**: From the re model,  $I_b = V_i / \beta$  re thus,

$$V_{o}$$

= -  $\beta$  ( $V_{i}$  /  $\beta$   $r_{e}$ ) (  $R_{C} \parallel r_{o}$ )

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{-R_{C}||r_{o}|}{r_{e}}$$

$$A_{v} = \frac{V_{o}}{V_{i}} \cong \frac{-R_{C}}{r_{e}}|r_{o} \ge 10R_{C}$$

Current gain:

$$A_{i} = \frac{I_{o}}{I_{i}} = \frac{\beta R_{B} r_{o}}{(r_{o} + R_{C})(R_{B} + \beta r_{e})}$$

$$A_{i} = \frac{I_{o}}{I_{i}} = \frac{\beta R_{B}}{(R_{B} + \beta r_{e})} \quad \text{if} \quad r_{o} \ge 10 R_{C}$$

$$A_{i} = \frac{I_{o}}{I_{i}} = \beta \quad \text{if} \quad R_{B} \ge 10 \beta r_{e}$$

$$A_{i} = -A_{v} \frac{Z_{i}}{R_{C}}$$

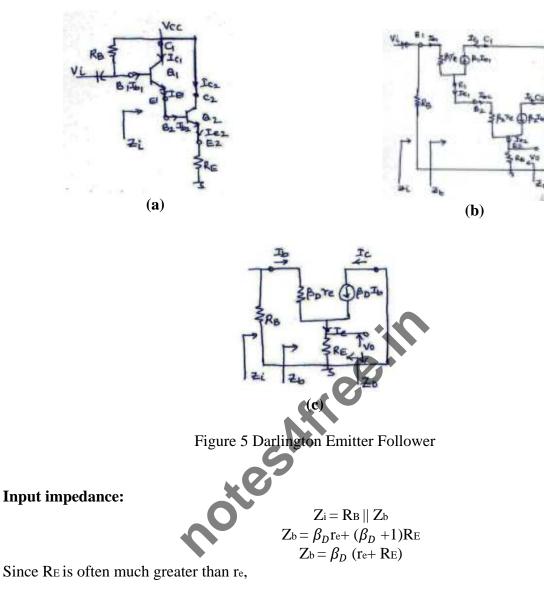

# **Common-Emitter Emitter-Bias Configuration**

Figure 4 Fixed bias Common-Emitter Configuration with un bypassed R<sub>E</sub>

### Input impedance:

Applying KVL to the input side:

$$V_i = I_b \beta r_e + I_e R_E$$

$V_i = I_b \beta r_e + (\beta + 1) I_b R_b$

Input impedance looking into the network to the right of RB is

$$Z_b = V_i / I_b = \beta r_e + (\beta + 1) R_E$$

Since  $\beta >>1$ ,  $(\beta +1) = \beta$

$$Z_b = V_i / I_b = \beta (r_e + R_E)$$

Since RE is often much greater than re,

$$Z_b = \beta R_E,$$

$$Z_i = R_B ||Z_b$$

**Output impedance:**  $Z_0$  is determined by setting V<sub>i</sub> to zero,  $I_b = 0$  and  $\beta$  I<sub>b</sub> can be replaced by open circuit equivalent. The result is,

$$Z_o = R_c$$

#### Voltage gain:

We know that,  $V_o = -I_oRc$ = -  $\beta I_bRc$ = -  $\beta (V_i/Z_b)Rc$  $Av = V_o / V_i = - \beta [Rc / (r_e + R_E)]$  $R_E >> r_e, Av = V_o / V_i = - \beta [Rc / R_E]$

Substituting,  $Z_b = \beta(r_e + R_E)$

$$A_{v} = \frac{V_{o}}{V_{i}} \approx \frac{-R_{c}}{r_{e} + R_{E}} | Z_{b} \Rightarrow \beta(r_{e} + R_{E})$$

$$A_{v} = \frac{V_{o}}{V_{i}} \approx \frac{-R_{c}}{R_{E}} | (r_{e} \ll R_{E})$$

$A_{v} = \frac{V_{o}}{V_{i}} = \frac{-R_{C}||r_{o}|}{Z_{b}}$

Phase relation: The negative sign in the gain equation reveals a 180<sub>o</sub> phase shift between input and output.

Current gain:

$$A_i = \frac{I_o}{I_i} = \frac{\beta R_B}{(R_B + Z_b)}$$

$$A_i = -A_v \frac{Z_i}{R_c}$$

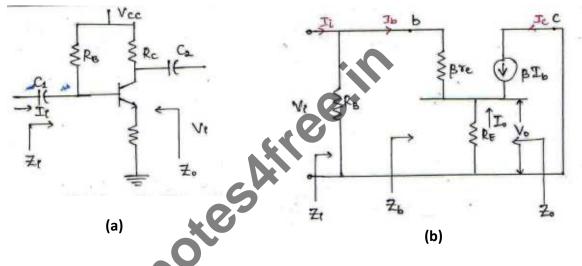

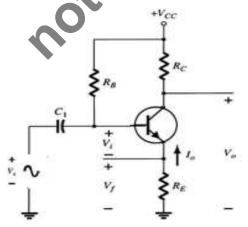

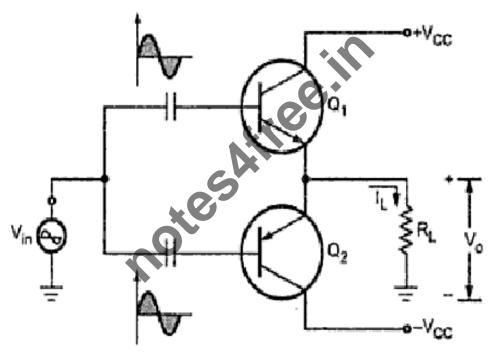

### **Darlington Emitter Follower**

This is also known as the common-collector configuration.

• The input is applied to the base and the output is taken from the emitter. There is no phase shift between input and output.

$$Z_i = R_B ||\beta r_e$$

$$Z_b = \beta_D (r_e + R_E)$$

### **Output impedance:**

To find Zo, it is required to find output equivalent circuit of the emitter follower at its input terminal.

This can be done by writing the equation for the current Ib.

$$I_{b} = V_{i} / Z_{b}$$

$$I_{e} = (\beta_{D} + 1)I_{b}$$

$$= (\beta_{D} + 1) (V_{i} / Z_{b})$$

We know that,  $Z_{b} = \beta_{D}r_{e} + (\beta_{D} + 1)RE$  substituting this in the equation for Ie we get,

$$I_{e} = (\beta_{D} + 1) (V_{i} / Z_{b}) = (\beta_{D} + 1) (V_{i} / \beta_{D}r_{e} + (\beta_{D} + 1)RE)$$

$$I_e = V_i / [\beta_D r_e / (\beta_D + 1)] + R_E$$

Since  $(\beta_D + 1) = \beta_D$ ,

$$I_e = V_i / [r_e + R_E]$$

Using the equation  $I_e = V_i / [r_e + R_E]$ , we can write the output equivalent circuit as,

$$Z_o = R_E || \frac{\beta_D r_e}{\beta_D + 1}$$

$Z_o \approx R_E ||r_e$  if  $\beta_D \gg 1$ Since RE is typically much greater than re,  $Z_o \approx r_e$

#### Voltage gain:

Using voltage divider rule for the equivalent circuit,

$$V_{o} = V_{i} R_{E} / (R_{E} + r_{e})$$

$$A_{v} = V_{o} / V_{i} = [R_{E} / (R_{E} + r_{e})]$$

0

Since  $(R_E + r_e) \cong R_E$ ,  $Av \cong [RE/(RE)] \cong 1$

Phase relationship As seen in the gain equation, output and input are in phase

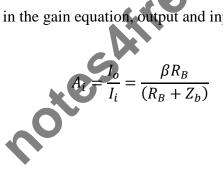

### **Current gain:**

### <u>H – Parameter model :-</u>

$\rightarrow$  The equivalent circuit of a transistor can be dram using simple approximation by retaining its essential features.

$\rightarrow$  These equivalent circuits will aid in analyzing transistor circuits easily and rapidly.

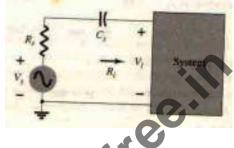

### Two port devices & Network Parameters:-

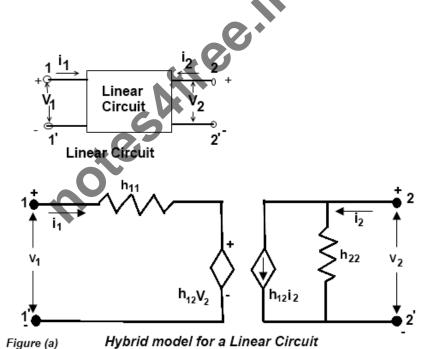

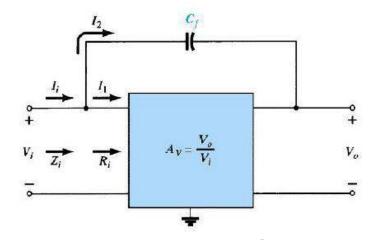

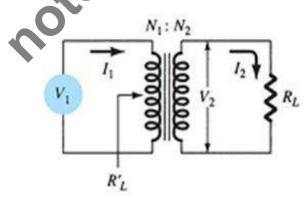

$\rightarrow$  A transistor can be treated as a two part network. The terminal behaviour of any two part network can be specified by the terminal voltages V<sub>1</sub> & V<sub>2</sub> at parts 1 & 2 respectively and current i<sub>1</sub> and i<sub>2</sub>, entering parts 1 & 2, respectively, as shown in figure.

Figure 6 Two port Network

### Hybrid parameters (or) h - parameters:-

If the input current  $i_1$  and output Voltage  $V_2$  are takes as independent variables, the input voltage  $V_1$  and output current  $i_2$  can be written as

$$\mathbf{V}_1 = \mathbf{h}_{11} \ \mathbf{i}_1 + \mathbf{h}_{12} \ \mathbf{V}_2$$

$i_2 \; = \; h_{21} \; i_1 + h_{22} \; V_2$

The four hybrid parameters  $h_{11}$ ,  $h_{12}$ ,  $h_{21}$  and  $h_{22}$  are defined as follows.

| $h_{11} = [V_1 / i_1]$ with $V_2 = 0$ | Input Impedance with output part short circuited.              |

|---------------------------------------|----------------------------------------------------------------|

| $h_{22} = [i_2 / V_2]$ with $i_1 = 0$ | Output admittance with input part open circuited.              |

| $h_{12} = [V_1 / V_2]$ with $i_1 = 0$ | reverse voltage transfer ratio with input part open circuited. |

| $h_{21} = [i_2 / i_1]$ with $V_2 = 0$ | Forward current gain with output part short circuited.         |

#### <u>The dimensions of h – parameters are as follows:</u>

h<sub>11</sub> - Ω

$h_{22}-mhos$

$h_{12}$ ,  $h_{21}$  – dimension less.

as the dimensions are not alike, (ie) they are hybrid in nature, and these parameters are called as hybrid parameters.

i = 11 = input; o = 22 = output;

f = 21 = forward transfer ; r = 12 Reverse transfer.

### Notations used in transistor circuits:-

$h_i = h_{11} = Short circuit input impedance$

$h_0 = h_{22} = Open$  circuit output admittance

$h_r = h_{12} = Open circuit reverse voltage transfer ratio$

$h_f = h_{21}$ = Short circuit forward current Gain.

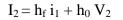

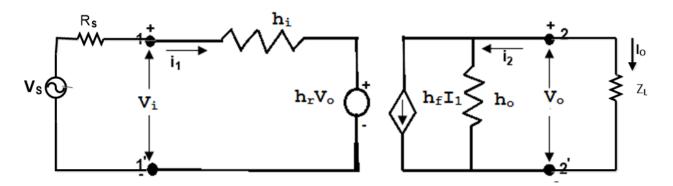

#### The Hybrid Model for Two-port Network:-

$$V_1 = h_{11} i_1 + h_{12} V_2$$

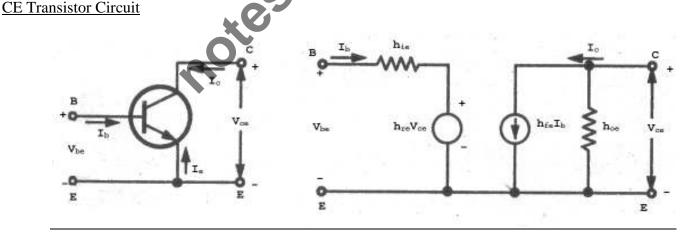

$$I_2 = h_1 i_1 + h_{22} V_2$$

$$V_1 = h_1 i_1 + h_r V_2$$

### Transistor Hybrid model:-

Essentially, the transistor model is a three terminal two – port system.

The h – parameters, however, will change with each configuration.

To distinguish which parameter has been used or which is available, a second subscript has been added to the h – parameter notation.

For the common – base configuration, the lowercase letter b is added, and for common emitter and common collector configurations, the letters e and c are used respectively.

Normally *h*ris a relatively small quantity, its removal is approximated by *h*r and hrvo = 0, resulting in a short – circuit equivalent.

The resistance determined by  $1/h_0$  is often large enough to be ignored in comparison to a parallel load, permitting its replacement by an open – circuit quivalent.

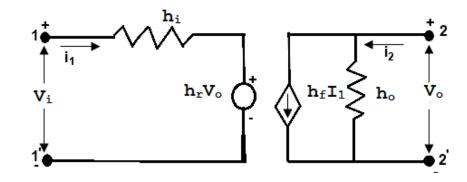

To Derive the Hybrid model for transistor consider the CE circuit shown in figure. The variables are  $i_{B,} i_c$ ,  $v_{B(=}v_{BE)}$  and  $v_{c(=}v_{CE)}$ .  $i_B$  and  $v_c$  are considered as independent variables.

Then,  $v_B = f_1(i_B, v_c)$  -----(1)

$i_{C} = f_2(i_{B}, v_c)$  -----(2)

Making a Taylor's series expansion around the quiescent point  $I_{B}$ ,  $V_{C}$  and neglecting higher order terms, the following two equations are obtained.

$$\Delta \mathbf{v}_{B} = (\partial f_{1}/\partial i_{B})\mathbf{V}_{c} \cdot \Delta i_{B} + (\partial f_{1}/\partial \mathbf{v}_{c})\mathbf{I}_{B} \cdot \Delta \mathbf{v}_{C} - \dots (3)$$

$$\Delta i_{C} = (\partial f_{2}/\partial i_{B})\mathbf{V}_{c} \cdot \Delta i_{B} + (\partial f_{2}/\partial \mathbf{v}_{c})\mathbf{I}_{B} \cdot \Delta \mathbf{v}_{C} - \dots (4)$$

The partial derivatives are taken keeping the collector voltage or base current constant as indicated by the subscript attached to the derivative.

$\Delta v_B$ ,  $\Delta v_C$ ,  $~\Delta~i_C$ ,  $\Delta~i_B$  represent the small signal(increment) base and collector voltages and currents,they are represented by symbols  $~v_b$ ,  $v_c$ ,  $i_b$  and  $~i_c$  respectively.

Eqs (3) and (4) may be written as

$$\begin{split} V_{b} &= h_{ie} i_{b} + h_{re} V_{c} \\ &i_{c} &= h_{fe} i_{b} + h_{oe} V_{c} \\ \end{split} \\ Where \quad h_{ie} &= (\partial f_{1} / \partial i_{B}) V_{c} = (\partial v_{B} / \partial i_{B}) V_{c} = (\Delta v_{B} / \Delta i_{B}) V_{c} = (v_{b} / i_{b}) V_{c} \\ &h_{re} &= (\partial f_{1} / \partial v_{c}) I_{B} = (\partial v_{B} / \partial v_{c}) I_{B} = (\Delta v_{B} / \Delta v_{c}) I_{B} = (v_{b} / v_{c}) I_{B} \\ &h_{fe} &= (\partial f_{2} / \partial i_{B}) V_{c} = (\partial i_{c} / \partial i_{B}) V_{c} = (\Delta i_{c} / \Delta i_{B}) V_{c} = (i_{c} / i_{b}) V_{c} \\ &h_{oe} &= (\partial f_{2} / \partial v_{c}) I_{B} = (\partial i_{c} / \partial v_{c}) I_{B} = (\Delta i_{c} / \Delta v_{c}) I_{B} = (i_{c} / v_{c}) I_{B} \end{split}$$

The above equations define the h-parameters of the transistor in CE configuration. The same theory can be extended to transistors in other configurations.

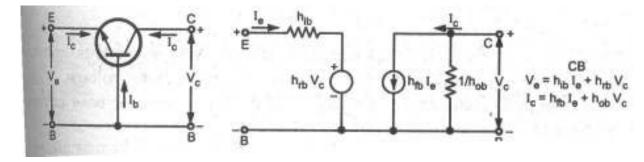

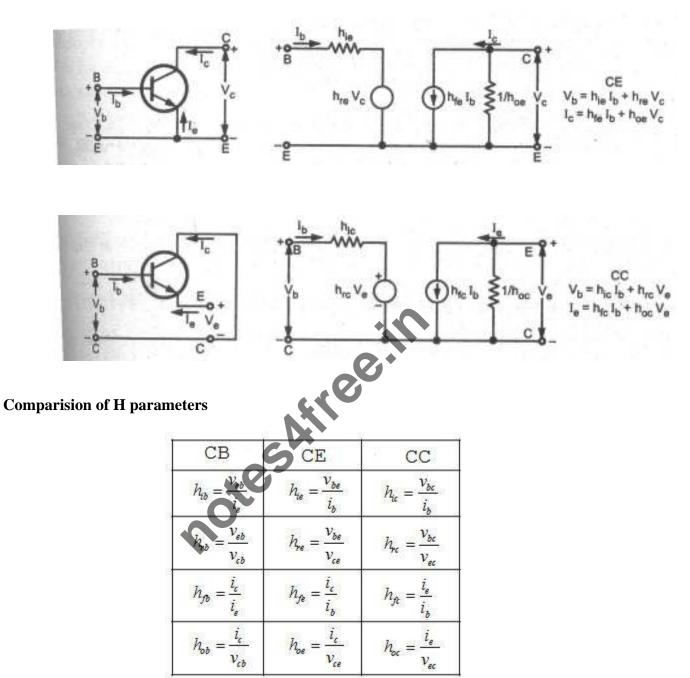

Hybrid Model and Equations for the transistor in three different configurations are are given below.

Analysis of transistor amplifier using h parameters.

For analysis of transistor amplifier we have to determine the following terms:

- Current Gain

- Voltage gain

- Input impedance

- Output impedance

### **Current gain:**

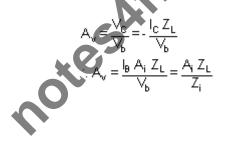

For the transistor amplifier stage,  $A_i$  is defined as the ratio of output to input currents.

$$\begin{array}{l} \mathsf{A}_{i}=\begin{array}{c} \frac{\mathsf{I}_{L}}{\mathsf{h}}=-\mathsf{I}_{0} \\ \mathsf{I}_{c}=\mathsf{I}_{h_{1}\mathsf{h}}\mathsf{h}_{b}+\mathsf{h}_{oe}\lor_{c} \\ \mathsf{V}_{a}=\mathsf{I}_{c}Z_{L}=-\mathsf{I}_{c}Z_{L} \\ \mathsf{I}_{c}=\mathsf{h}_{fe}:\mathsf{I}_{b}+\mathsf{h}_{oe}:(\mathsf{I}_{c}:Z_{L}) \\ \mathsf{or}:=\operatorname{h}_{fe}:\mathsf{I}_{b}+\mathsf{h}_{oe}:(\mathsf{I}_{c}:Z_{L}) \\ \mathsf{or}::\operatorname{I}_{b}:=\frac{\mathsf{h}_{fe}}{\mathsf{I}+\mathsf{h}_{oe}:Z_{L}} \\ \therefore \mathsf{A}_{i}=-\begin{array}{c} \frac{\mathsf{h}_{fe}}{\mathsf{I}+\mathsf{h}_{oe}:Z_{L}} \end{array}$$

00'

# **Input Impedence:**

The impedence looking into the amplifier input terminals ( 1,1' ) is the input impedence  $Z_i$

$$\begin{aligned} Z_i &= \frac{V_b}{I_b} \\ V_b &= h_{ie} I_b + h_{re} V_c \\ \frac{V_b}{I_b} &= h_{ie} + h_{re} \frac{V_c}{I_b} \\ &= h_{ie} - \frac{h_{re} I_c Z_L}{I_b} \\ \therefore Z_i &= h_{ie} + h_{re} A_1 Z_L \\ &= h_{ie} - \frac{h_{re} h_{fe} Z_L}{1 + h_{oe} Z_L} \\ \therefore Z_i &= h_{ie} - \frac{h_{re} h_{fe} Z_L}{Y_L + h_{oe}} \end{aligned}$$

(since  $Y_L = \frac{1}{Z_L}$ )

# Voltage gain:

The ratio of output voltage to input voltage gives the gain of the transistors.

### **Output Admittance: It is defined**

$$\begin{split} Y_0 &= \frac{I_c}{V_c} \bigg|_{V_s} = 0 \\ I_c &= h_{fe}I_b + h_{oe} \ V_c \\ \frac{I_c}{V_c} &= h_{fe} \frac{I_b}{V_c} + h_{oe} \\ when \ V_s = 0, \qquad R_s.I_b + h_{ie}.I_b + h_{re} \ V_c = 0 \\ \frac{I_b}{V_c} &= -\frac{h_{re}}{R_s + h_{ie}} \\ \therefore \ Y_0 &= h_{oe} - \frac{h_{re} \ h_{fe}}{R_s + h_{ie}} \end{split}$$

Voltage amplification taking into account source impedance (R<sub>S</sub>) is given by

Simplified Hybrid model is identical to the remodel is as shown in fig. refer re model analysis

## Hybrid versus re model: (a) common-emitter configuration

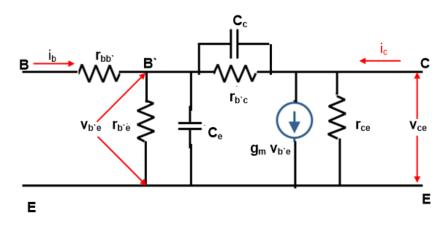

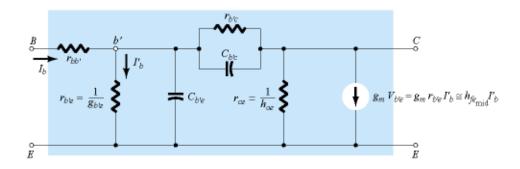

### Hybrid $\cdot \pi$ model

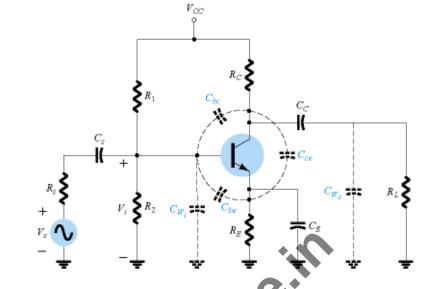

- The hybrid-pi or Giacoletto model of common emitter transistor model is given below. The resistance components in this circuit can be obtained from the low frequency hparameters.

- For high frequency analysis transistor is replaced by high frequency hybrid-pi model and voltage gain, current gain and input impedance are determined.

This is more accurate model for high frequency effects. The capacitors that appear are stray parasitic capacitors between the various junctions of the device. These capacitances come into picture only at high frequencies.

- Cbc or Cu is usually few pico farads to few tens of pico farads.

- rbb includes the base contact, base bulk and base spreading resistances.

- $r_{be}$  ( $r_{\pi}$ ),  $r_{bc}$ ,  $r_{ce}$  are the resistances between the indicated terminals.

- $r_{be}(r_{\pi})$  is simply  $\beta r_{e}$  introduced for the CE  $r_{e}$  model.

- rbc is a large resistance that provides feedback between the output and the input.

- $r_{\pi} = \beta r_e$

- $g_m = 1/r_e$

- $r_o = 1/h_{oe}$

- hre =  $r_{\pi}/(r_{\pi}+r_{bc})$

The **transconductance**, **gm**, is related to the dynamic (differential) resistance, re, of the forwardbiased emitter-base junction:

$g_{m} = \partial Ic/\partial Vb' e$  $= \alpha \partial Ie/\partial Vb' e$  $\approx \alpha / re$  $\approx Ic/Vth$

Vth = kBT/q

The resistance rbb' is the base spreading resistance.

The resistance rb'c and the capacitance Cb'c (Cc) represent the dynamic (differential) resistance and the capacitance of the reverse-biased collector-base junction.

Using transconductance:

ic  $\approx$  gm vb'e (ignoring the current through  $r_{ce}$  )

noteshireetin

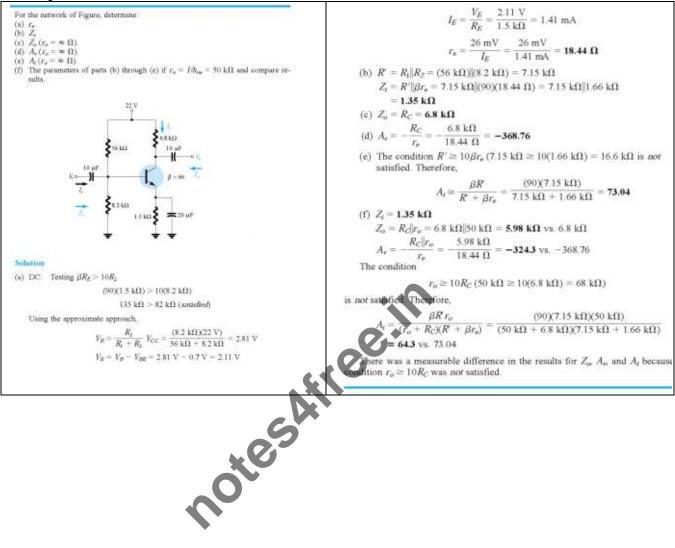

(a) Determine  $r_e$ . (b) Find Z<sub>i</sub> (c) Calculate Z<sub>0</sub> (d) Determine A<sub>v</sub> (e) Find A<sub>i</sub> (f) Repeat parts (c) through (e) including  $r_0 = 50 \text{ k}\Omega$  in all calculations and compare results. (From Text Book - Boylestad)

which differs slightly only due to the accuracy carried through the calculations.

#### Solution

(a) DC:

$$I_B = \frac{V_{CC} - V_{BE}}{R_B + (\beta + 1)R_E} = \frac{20 \text{ V} - 0.7 \text{ V}}{470 \text{ k}\Omega + (121)0.56 \text{ k}\Omega} = 35.89 \ \mu\text{A}$$

$I_E = (\beta + 1)I_B = (121)(46.5 \ \mu\text{A}) = 4.34 \text{ mA}$

and  $r_e = \frac{26 \text{ mV}}{I_E} = \frac{26 \text{ mV}}{4.34 \text{ mA}} = 5.99 \ \Omega$

(b) Testing the condition  $r_o \ge 10(R_C + R_E)$ ;

$40 \text{ k}\Omega \ge 10(2.2 \text{ k}\Omega + 0.56 \text{ k}\Omega)$

$40 \text{ k}\Omega \ge 10(2.76 \text{ k}\Omega) = 27.6 \text{ k}\Omega \ (satisfied)$

Therefore,

$Z_b \cong \beta(r_0 + R_E) = 120(5.99 \ \Omega + 560 \ \Omega)$

$= 67.92 \text{ k}\Omega$

and

$Z_I = R_B \|Z_b = 470 \text{ k}\Omega\| 67.92 \text{ k}\Omega$

(c)

$$Z_o = R_C = 2.2 \text{ k}\Omega$$

(d)

$$r_o \ge 10 R_C$$

is satisfied. Therefore,

$$A_{v} = \frac{V_{o}}{V_{i}} \cong -\frac{\beta R_{C}}{Z_{b}} = -\frac{(120)(2.2 \text{ k}\Omega)}{67.92 \text{ k}\Omega}$$

= -3.89

compared to -3.93 using Eq. (8.27):  $A_v \approx -R_C/R_E$

(e)

$$A_i = -A_v \frac{Z_i}{R_c} = -(-3.89) \left( \frac{59.34 \text{ k}\Omega}{2.2 \text{ k}\Omega} \right)$$

= 104.92

compared to 104.85 using Eq. (8.28):  $A_I \cong \beta R_B / (R_B + Z_b)$ .

Repeat the analysis of Example 3 with  $C_E$  in place.

#### Solution

(a) The dc analysis is the same, and  $r_e = 5.99 \ \Omega$ .

$$Z_{I} = R_{B} ||Z_{b} = R_{B} ||\beta r_{e} = 470 \text{ k}\Omega ||(120)(5.99 \Omega)$$

= 470 k\Omega ||718.8 \Omega \approx 717.70 \Omega

(c)

$$Z_o = R_C = 2.2 \text{ k}\Omega$$

(d)  $A_v = -\frac{R_C}{r_o}$

$= -\frac{2.2 \text{ k}\Omega}{5.99 \Omega} = -367.28$  (a significant increase)

(e)  $A_I = \frac{\beta R_B}{R_B + Z_o} = \frac{(120)(470 \text{ k}\Omega)}{470 \text{ k}\Omega + 718.8 \Omega}$

$= 119.82$

noteshireeth

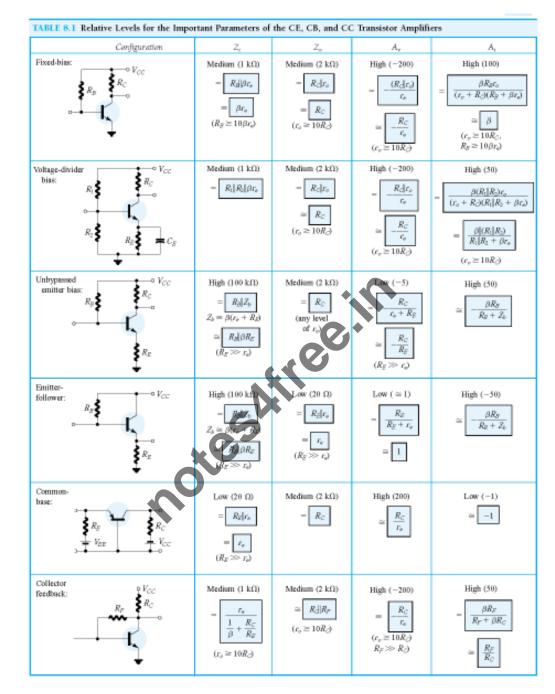

### **Summary of Transistor small signal analysis**

8.12 Troubleshooting

383

### FORMAT-1B

# MODULE-2: Field Effect Transistors (FET)

### **Definition:**

FET is a three terminal electronic device used for variety of applications that match with BJT. In FET, an electric field is established by the charges present, which controls the conduction path of the output circuit without the need for direct contact between controlling and controlled quantities. In a Field effect device current is controlled by the action of an electron field, rather than carrier injection.

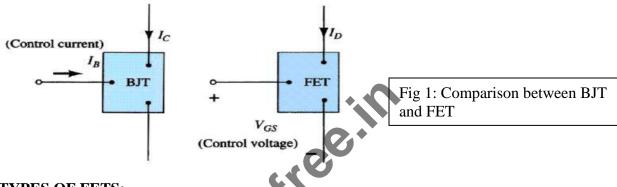

The main difference between BJT and FET is BJT is a current controlled device while FET is a voltage controlled device. This is shown in fig 1.

### **TYPES OF FETS:**

- 1. Junction Field Effect Transistors(JFETs)

- 2. Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)

# JUNCTION FIELD EFFECT TRANSISTORS(JFETS):

JFET is a unipolar device as conduction in the device is dependent on either electrons or holes. Accordingly there are two types of JFET; namely: n-Channel JFET and p-Channel JFET.

### **Features of FET:**

- FET is a voltage controlled device.

- FET is a unipolar device.

- FET has high input impedance

- AC voltage gain of JFET is low

- FET has higher temperature stability.

- FET are small in size and hence are useful in ICs.

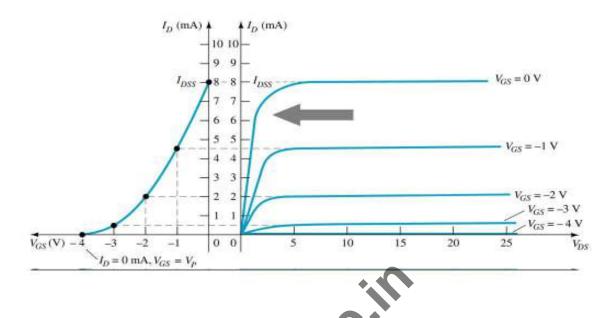

### CONSTRUCTION AND CHARACTERISTICS OF N-CHANNEL JFET:

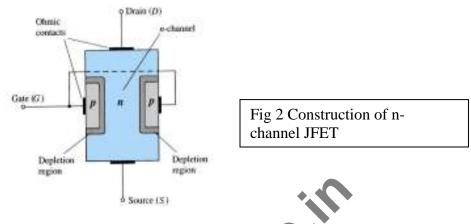

The basic construction of the n-channel JFET is as shown in fig 2. The major part of the structure is the n-type material which forms the channel between embedded layers of p-

type material. The top of the n-type channel is connected through an ohmic contact to a terminal referred to as the drain(D), where as the lower end of the material is connected through an ohmic contact referred to as source(S). The 2 p-type materials are connected together to the gate (G) terminal. In the absence of any applied potentials , JFET has 2 p-n junctions under no bias condition. As a result, depletion region is formed at each junction.

### **OPERATION:**

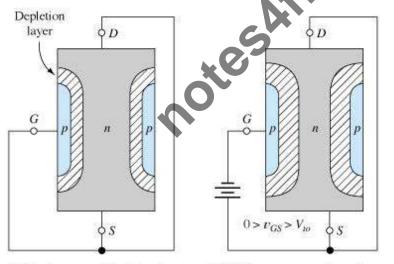

Fig 3 shows the working of n-channel JFET for different gate-source voltage ( $V_{GS}$ ) and drain to source voltage ( $V_{DS}$ ) = 0V.

(a) Bias is zero and depletion layer is thin; low-resistance channel exists between the drain and the source

(b) Moderate gate-to-channel reverse bias results in narrower channel

(c) Bias greater than pinch-off voltage; no conductive path from drain to source

$v_{GS} < V_{10}$

G

φD

n

05

Fig 3: Operation of n-channel JFET

Case i:  $V_{GS} = 0$  and  $V_{DS} = 0$

• Under zero bias condition depletion region around the p-n junction is thin and thus exhibits low channel resistance.

### Case ii: $V_{GS} = 0$ and $V_{DS} = +$ small voltage.

The gate and source are at the same potential and the instant the voltage VDS is applied the electrons in the n-channel are drawn towards the drain terminal establishing drain current (ID).

Due to reverse biasing of the p-n junction for the length of the channel results in gate current = 0.

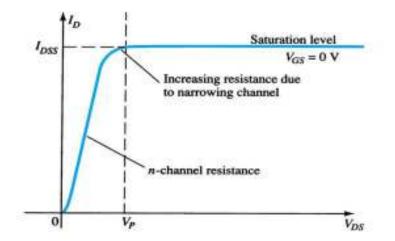

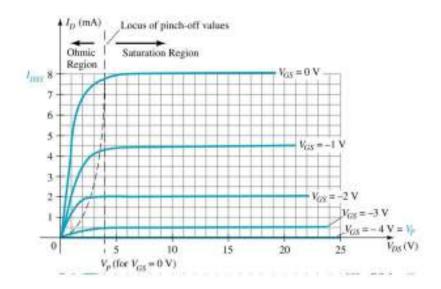

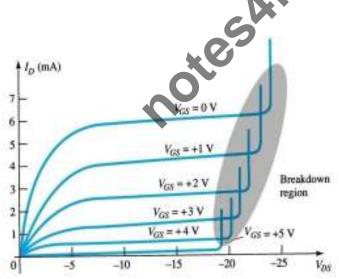

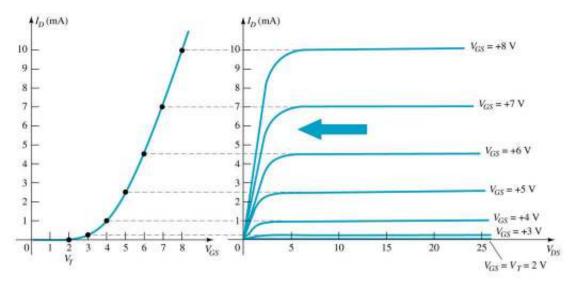

As VDS is increased further, the drain current increases. When VDS = VP, the depletion region widens causing reduction in the channel width. The reduced path of conduction causes the resistance to increase and the current saturates. When VDS is further increased, the two deletion regions touch resulting in pinch-off condition. The drain characteristics (plot of ID vs VDS for VGS = constant is as shown in fig 4.

### Case iii: $V_{GS}$ = -ve voltage and $V_{DS}$ = + small voltage.

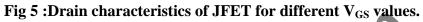

The effect of applied reverse bias on gate and source widens the depletion regions around the p-n junctions but at the lower levels of VDS. The resulting saturation level for ID is reduced and will continue to decrease as VGS is made more and more negative. The drain characteristics is as shown in fig 5 for different values of VGS. When VGS = -VP, pinch-off condition occurs resulting in ID = 0. VP is called pinch-off voltage.

The region to the left of pinch off locus is called ohmic region and the region to the right of pinch-off locus is saturation region. This region of JFET is employed for linear amplifiers. In ohmic region JFET can be employed as a variable resistor. The resistance is controlled by VGS. As VGS becomes more and more negative , the slope of the characteristics becomes more and more horizontal indicating increasing resistance level.

The resistance is given by the equation 1.

Fig 4 : Drain characteristics of n-channel JFET for VGS = 0V.

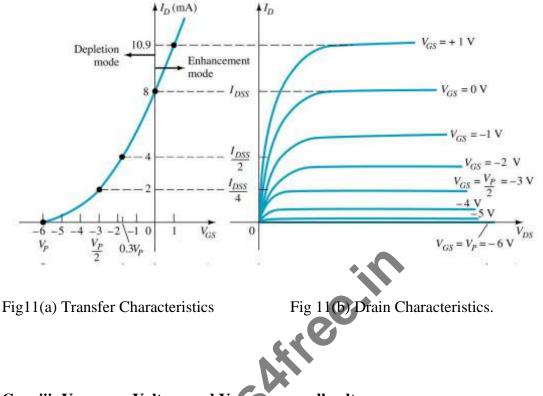

# TRANSFER CHARACTERISTICS OF N-CHANNEL JFET:

Transfer characteristics are a plot of  $I_D$  as a function of  $V_{GS}$  with  $V_{DS}$  as constant. Shockley Equation as in equation 1 is used to plot transfer characteristics.

$I_D$  depends on  $V_{GS}$  in a non-linear manner. As a result, FET's are often referred to square law devices. Using the drain characteristics on the right of Y-axis, we can draw a horizontal line from the saturation region of the curve denoted as  $V_{GS} = 0V$  to the  $I_D$  axis. The resulting current level for both the graphs is  $I_{DSS}$ .

When  $V_{GS} = V_P$ , the drain current is 0mA, defining another point on transfer curve. Transfer curve is a direct transfer from input to output variables. Transfer characteristics are a parabolic curve as shown in fig 6.

Fig 6: Transfer characteristics from drain characteristics

### TRANSFER CHARACTERISTICS: SHORT-HAND METHOD

Transfer characteristics can also be obtained by applying following conditions to schokley's equation (1). Condition1: VGS = 0

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right)^{2}$$

Therefore  $I_D = I_{DSS}$ .

Condition  $2:V_{GS} = V_P$

Therefore from equation 1  $I_D = 0mA$ .

Condition 3:  $V_{GS} = V_P/2$ Therefore from equation 1, $ID = IDSS(1 - \frac{1}{2})^{-2}$  $I_D = I_{DSS}/4$ Condition 4:  $I_D = I_{DSS}/2$

From eq(1),  $VGS = VP(1 - \sqrt{ID/IDSS})$

$$VGS = VP(1 - \sqrt{0.5})$$

$$VGS = 0.3VP$$

Points are marked for these conditions of VGS and ID and the co-ordinates are joined using smooth curve.

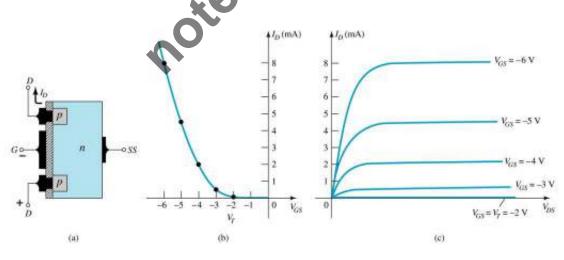

#### **CONSTRUCTION AND CHARACTERISTICS OF P-CHANNEL JFET:**

The basic construction of the p-channel JFET is as shown in fig 2. The major part of the structure is the p-type material which forms the channel between embedded layers of p-type material. The top of the p-type channel is connected through an ohmic contact to a terminal referred to as the drain(D), where as the lower end of the material is connected through an ohmic contact referred to as source(S). The 2 n-type materials are connected together to the gate (G) terminal. In the absence of any applied potentials , JFET has 2 p-n junctions under no bias condition. As a result, depletion region is formed at each junction.

Fig 7 Construction of n- channel JFET

#### **OPERATION OF P-CHANNEL JFET:**

Case i:  $V_{GS} = 0$  and  $V_{DS} = 0$

• Under zero bias condition depletion region around the p-n junction is thin and thus exhibits low channel resistance.

### Case ii: $V_{GS} = 0$ and $V_{DS} =$ -ve small voltage.

The gate and source are at the same potential and the instant the voltage VDS is applied the holes in the p-channel are drawn towards the drain terminal establishing drain current (ID).

Due to reverse biasing of the p-n junction for the length of the channel results in gate current = 0.

As VDS is increased further, the drain current increases. When VDS = -VP, the depletion region widens causing reduction in the channel width. The reduced path of conduction causes the resistance to increase and the current saturates. When VDS is further increased, the two deletion regions touch resulting in pinch-off condition. The drain characteristics (plot of ID vs VDS for VGS = constant is as shown in fig 8).

### Case iii: $V_{GS}$ = +ve voltage and $V_{DS}$ = -ve small voltage.

The effect of applied reverse bias on gate and source widens the depletion regions around the p-n junctions but at the lower levels of VDS. The resulting saturation level for ID is reduced and will continue to decrease as VGS is made more and more positive. The drain characteristics are as shown in fig 8 for different values of VGS. When VGS = -VP, pinch-off condition occurs resulting in ID = 0. VP is called pinch-off voltage.

Fig 8: Drain Characteristics of p-channel JFET

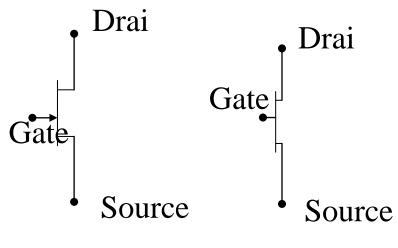

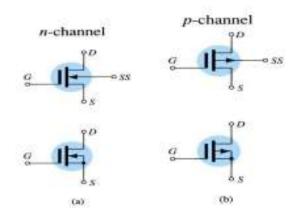

### Symbols of JFET: Fig 9(a) and 9 (b) shows the symbols of n-channel and p- channel FET respectively.

Fig 9: JFET Symbols. 9(a) n-Channel JFET

9(b)p-channel JFET

# Metal Oxide Semiconductor Field Effect Transistors (MOSFETs):

MOSFET is a type of Field Effect Transistor in which majority charge carriers flow in the channel. The width of the channel is controlled by an electrode called gate. Channel width determines how well the device conducts.

MOSFETS are useful in high-speed switching circuits and in Integrated Circuits.

There are two types of MOSFET's:

- (i) Depletion type MOSFET

- (ii) Enhancement type MOSFET

### **DEPLETION TYPE MOSFET:**

Depletion-type MOSFETs are further classified as

- (i) N-channel D-type MOSFET

- (ii) P-Channel D-type MOSFET

### **N-CHANNEL DEPLETION TYPE MOSFET:**

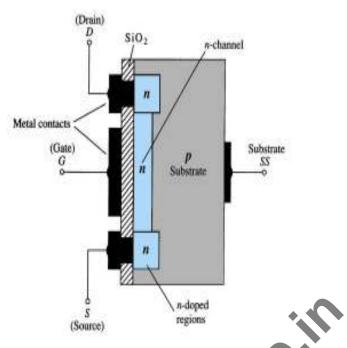

The basic construction of the n-channel depletion type MOSFET is as shown in fig (10). A slab of p-type material is formed from a Si base and is referred to as the substrate. The source and drain terminals are connected through metallic contacts to n-doped regions linked by a n-channel. The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin SiO<sub>2</sub> layer. The presence of SiO<sub>2</sub> layer accounts for very high input impedance of the device. The input impedance of MOSFET is higher than JFET.

Fig 10: Construction n-Channel Depletion type MOSFET

A small n layer is implanted in the region below  $SiO_2$  to create n-channel. The insulating layer between gate and the channel has resulted in another name for the device : Insulated-gate FET or IGFET.

# **OPERATION OF N-CHANNEL DEPLETION MODE MOSFET:**

## Case i: $V_{GS} = 0$ and $V_{DS} = +ve$ voltage

Since drain is positive with respect to source, the free electrons are attracted from source to drain to constitute drain current  $I_D$ . The drain characteristics and transfer characteristics of depletion mode MOSFET is as shown in fig 11.

### Case ii: $V_{GS}$ = -ve Voltage and $V_{DS}$ = +ve small voltage

The negative potential at the gate will cause the electrons to move towards p-type substrate as charges repel while holes from p-type substrate are attracted toward gate. Depending on the magnitude of negative bias established by  $V_{GS}$ , a level of recombination between electrons and holes will occur that will reduce the number of free electrons in the n-channel available for conduction. The more negative the bias, higher is the rate of recombination. The resulting level of  $I_D$  is reduced with the increasing levels og negative bias for VGS as in fig11.

# Case iii: $V_{GS}$ = +ve Voltage and $V_{DS}$ = +ve small voltage

For positive values of  $V_{GS}$ , the +ve gate will draw additional electrons from p-type substrate as minority charge carriers are attracted towards gate. New carriers are generated due to collisions and  $I_D$  will increase at a rapid rate. Thus, application of + $V_{GS}$  has enhanced the level of free carriers in the channel compared to  $V_{GS} = 0V$ . The region of +ve gate voltage on the drain or transfer characteristics is referred as enhancement region. The region between the cut-off and the saturation level of  $I_{DSS}$  is referred as the depletion region.

Transfer characteristics are a plot of  $I_D$  as a function of  $V_{GS}$  with  $V_{DS}$  as constant. Shockley Equation as in equation 2 is used to plot transfer characteristics.

----- Eqn (2)

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

Also, Short hand method can be used to plot transfer characteristics curve.

Condition1:  $V_{GS} = 0$ , Hence from eq(2),

$I_{\rm D} = I_{\rm DSS}.$

Condition  $2:V_{GS} = V_P$

Therefore from equation  $2 I_D = 0 m A$ .

Condition 3:  $V_{GS} = V_P/2$ Therefore from equation 2,  $ID = IDSS(1 - \frac{1}{2})^{-2}$   $I_D = I_{DSS}/4$ Condition 4:  $I_D = I_{DSS}/2$ From eq(1),  $VGS = VP(1 - \sqrt{ID/IDSS})$   $VGS = VP(1 - \sqrt{0.5})$  VGS = 0.3VPVGS = 0.3VP

Points are marked for these conditions of VGS and ID and the co-ordinates are joined using smooth curve.

# P-CHANNEL DEPLETION TYPE MOSFET:

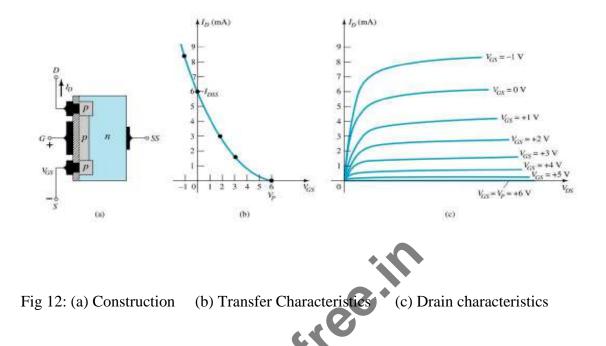

The basic construction of the p-channel depletion type MOSFET is as shown in fig (12a). A slab of n-type material is formed from a Si base and is referred to as the substrate. The source and drain terminals are connected through metallic contacts to p-doped regions linked by a p-channel. The gate is also connected to a metal contact surface but remains insulated from the p-channel by a very thin  $SiO_2$  layer. The presence of  $SiO_2$  layer accounts for very high input impedance of the device. The input impedance of MOSFET is higher than JFET.

# **OPERATION OF P-CHANNEL DEPLETION MODE MOSFET:**

### Case i: $V_{GS} = 0$ and $V_{DS} = -ve$ voltage

Since drain isnegative with respect to source, the holes are attracted from source to drain to constitute drain current  $I_D$ . The drain characteristics and transfer characteristics of depletion mode MOSFET is as shown in fig 12(c) and (b) respectively.

#### Case ii: $V_{GS}$ = +ve Voltage and $V_{DS}$ = -ve small voltage

The positive potential at the gate will cause the holes to move towards n-type substrate as charges repel while electrons from n-type substrate are attracted toward gate. Depending on the magnitude of positive bias established by  $V_{GS}$ , a level of recombination between electrons and holes will occur that will reduce the number of holes in the p-channel available for conduction. The more positive the bias, higher is the rate of recombination. The resulting level of  $I_D$  is reduced with the increasing levels or positive bias for  $V_{GS}$  as in fig12(c).

#### Case iii: $V_{GS}$ = -ve Voltage and $V_{DS}$ = -ve small voltage

For positive values of  $V_{GS}$ , the -ve gate will draw additional holes from n-type substrate as minority charge carriers are attracted towards gate. New carriers are generated due to

collisions and I<sub>D</sub> will increase at a rapid rate. Thus, application of -V<sub>GS</sub> has enhanced the level of free carriers in the channel compared to  $V_{GS} = 0V$ .

Transfer characteristics are a plot of  $I_D$  as a function of  $V_{GS}$  with  $V_{DS}$  as constant. Shockley Equation as in equation 2 is used to plot transfer characteristics.

----- Eqn (3) ID = IDSS

$$\left(1 - \frac{V_{GS}}{V_P}\right)^2$$

Also, Short hand method can be used to plot transfer characteristics curve.

Condition1:  $V_{GS} = 0$ , Hence from eq(3),

$I_D = I_{DSS}$ .

iree.in Condition  $2:V_{GS} = V_P$ Therefore from equation  $2 I_D = 0 m A$ . Condition 3:  $V_{GS} = V_P/2$ Therefore from equation 2,ID = IDS $I_D = I_{DSS}/4$ Condition 4:  $I_D = I_{DSS}/2$  $P(1 - \sqrt{ID/IDSS})$ From eq(1), VGS  $VGS = VP(1 - \sqrt{0.5})$ VGS = 0.3VPVGS = 0.3VP

Points are marked for these conditions of V<sub>GS</sub> and I<sub>D</sub> and the co-ordinates are joined using smooth curve.

#### SYMBOLS OF DEPLETION TYPE MOSFET

Fig 13 shows the symbols of n-channel and p-channel Depletion mode MOSFET.

Fig 13 (a) n-channel depletion type MOSFET (b) p-channel depletion type MOSFET

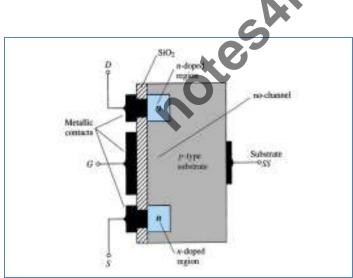

#### N-CHANNEL ENHANCEMENT-MODE MOSFET (E-MOSFET):

The construction of n-channel enhancement mode MOSFET is as shown in fig 14. The starting material is a p-type substrate into which highly doped n-regions are diffused to form source and drain regions. A layer of  $SiO_2$  is grown allover the p-type substrate and is etched to create window for n-diffusion. The source and drain terminals are taken out through metallic contacts to n-doped regions as shown in fig 14. Metal is deposited on SiO2 to create Gate. The presence of SiO2 between gate and p-substrate provides electrical isolation between the two regions. No channel exists between source and drain in E-MOSFET.

Fig 14: Construction of n-channel E-MOSFET

### **OPERATION OF N-CHANNEL E-MOSFET:**

Case i:  $V_{GS} = 0$  and  $V_{DS} = +ve$  voltage

The application of drain to source voltage while gate and source are shorted will cause no ID to flow as no channel exists for this condition.

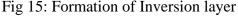

#### Case ii: $V_{GS}$ = +ve Voltage and $V_{DS}$ = +ve small voltage

When gate is made positive with respect to source, electrons are attracted towards the gate but holes are repelled back into p-type substrate. Since the region under the gate is ptype substrate, the positive voltage on gate causes holes which are majority charge carriers in p-type substrate to repel and move towards substrate. A positive V<sub>GS</sub> and positive  $V_{DS}$  causes the two pn junctions to be reverse biased and depletion region is formed. Now the device is said to be in depletion mode. The positive  $V_{GS}$  also causes electrons to be attracted towards the gate. Now, device is said to be in accumulation mode. Since the region below the gate was p-substrate and accumulation of electrons has caused the type to change to n-type. Thus the device is said to be in inversion mode as shown in fig 15. A positive  $V_{GS}$  has caused a thin layer of negative chargesto be formed in the substrate under the gate. Thus, channel is said to be created. The value of  $V_{GS}$ which causes channel to be formed under the gate is called threshold  $voltage(V_T)$ . A small I<sub>D</sub> flows. When V<sub>GS</sub> is increased above V<sub>T</sub>, conductivity of the channel is enhanced and thus pulling more electrons into the channel. When  $V_{GS} < V_T$ , there is no channel. Since channel is formed by the application of  $+V_{GS}$ , the type of MOSFET is Enhancement type. As  $V_{GS}$  is increased further, higher level of  $I_D$  flows as shown in fig 16. A positive  $V_{GS}$  cause potential drop across the channel. For large  $V_{DS}$  this voltage may not be sufficient to invert the channel near the drain end there by causing drain current to saturate. The channel is said to be pinched off. I<sub>D</sub> flows due to diffusion.

#### TRANSFER CHARACTERISTICS OF N-CHANNELE-MOSFET:

The transfer characteristics of n-channel E-MOSFET is as shown in fig 16. For VGS >VT, the relationship between drain current and VGS is nonlinear and is given by eqn 4.  $ID = K(VGS - VT)^{-2}$  -----Eq 4 Where K is a constant and is a function of the construction of the device as given by Eqn 5.

$$K = \frac{ID(ON)}{(VGS(ON) - VT)^{-2}} \qquad \text{------Eq 5}$$

Fig16: Transfer Characteristics

**Drain Characteristics**

Thus  $I_D$  increases steadily when  $V_{GS} > V_T$  and  $I_D$  is zero when  $V_{GS} < V_T$ .

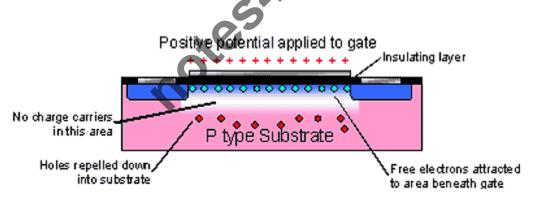

# p-CHANNELENHANCEMENT-MODE MOSFET (E-MOSFET):

The construction of p-channel E-MOSFET is opposite to that of n-channel E\_MOSFET. Substrate is of n-type and source, drain are of p-type as in fig17(a). The voltage polarities and current directions are reversed in p-channel E-MOSFET. The drain and transfer characteristics of p-channel E-MOSFET are as shown in Fig 17 (c) and (b) respectively.

Fig 17: (a) Construction (b) 7

(b) Transfer Characteristics

(c) Drain Characteristics

### **OPERATION OF P-CHANNEL E-MOSFET:**

#### Case i: $V_{GS} = 0$ and $V_{DS} = -ve$ voltage

The application of drain to source voltage while gate and source are shorted will cause no ID to flow as no channel exists for this condition.

#### Case ii: $V_{GS}$ = -ve Voltage and $V_{DS}$ = -ve small voltage

When gate is made negative with respect to source, holes are attracted towards the gate but electrons are repelled back into n-type substrate. Since the region under the gate is ntype substrate, the negative voltage on gate causes electrons which are majority charge carriers in n-type substrate to repel and move towards substrate. A negative V<sub>GS</sub> and negative V<sub>DS</sub> causes the two pn junctions to be reverse biased and depletion region is formed. Now the device is said to be in depletion mode. The negative  $V_{GS}$  also causes holes to be attracted towards the gate. Now, device is said to be in accumulation mode. Since the region below the gate was n-substrate and accumulation of holes has caused the type to change to p-type. Thus the device is said to be in inversion mode .A negative  $V_{GS}$ has caused a thin layer of positive charges to be formed in the substrate under the gate. Thus, channel is said to be created. The value of  $V_{GS}$  which causes channel to be formed under the gate is called threshold  $voltage(V_T)$ . A small  $I_D$  flows. When  $V_{GS}$  is decreasedbelow V<sub>T</sub>, conductivity of the channel is enhanced and thus pulling more electrons into the channel. When  $V_{GS}>V_T$ , there is no channel. Since channel is formed by the application of -V<sub>GS</sub>, the type of MOSFET is Enhancement type. The drain characteristics are as shown in fig 17 (c).

### TRANSFER CHARACTERISTICS OF P-CHANNEL E-MOSFET:

The  $V_{GS}$  is negative and  $I_D$  flows in opposite direction. The transfer characteristics of pchannel E-MOSFET is as shown in fig 17(b).  $I_D$  increases steadily with  $V_{GS}$ .

### **E-MOSFET SYMBOLS:**

Fig 18 (a) and 18(b) shows the symbols of n-channel and p-channel E-MOSFET.

Fig 18: E-MOSFET Symbols

#### FET CONFIGURATION:

The three types of FET configuration are:

- (i) Common Source (CS) Configuration

(ii) Common Drain (CD) Configuration

- (iii)Common Gate (CG) Configuration

#### FET BIASING:

Biasing is done to establish proper levels of DC voltages and currents for desired region of operation. It establishes Q-point.

### **TYPES OF BIASING:**

- (i) Fixed Bias

- (ii) Self Bias

- (iii)Voltage divider Bias

Voltage divider bias most widely used biasing technique in amplifiers.

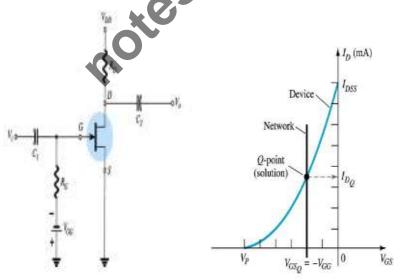

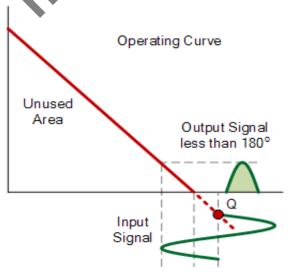

#### FET AS AN AMPLIFIER:

Fig.19 Shows Common Source Circuit. The Voltage  $V_{GG}$  provides the necessary reverse-bias between gate and source of JFET. The signal to be amplified is  $V_S$ . The transfer Characteristics of JFET is as shown in Fig. 20. A DC load line is drawn on the characteristics. The point of intersection of DC load line on Transfer characteristics for specific  $V_{GS}$  is called Q point. Let Q point be situated at the middle of DC load line.

Fig 19: CS Amplifier with Fixed Bias

Fig 20: Locate Q-Point

The instantaneous  $V_{gs}$  is  $V_{gs}=V_S-V_{GG}$  ----- (6) Both  $I_D$  and  $V_{DS}$  can be considered as sinusoid superimposed on the DC values.

Then  $V_{GS} = -V_{GG} + V_{gs} - ---- (7)$  $I_D = i_d + I_{DQ}$  $V_{OUT} = V_{DS} = V_{DSO} + V_{ds} - \dots (8)$ Since output signal is greater than input signal, amplification has occurred. The magnitude of Voltage gain is the ratio of output voltage to input voltage.

$|A_V| = \frac{V_O}{V_S}$

The selection of Q point at the middle gives undistorted output. If the operating point is located either closer to ohmic region or near pinch-off voltage, the output waveform will be clipped during +Ve or -Ve half cycles. In Common Source circuit, output is 180<sup>0</sup> out of phase with input.

To locate Q point, the following procedure is used

- Plot transfer characteristics

- Draw a vertical line(load line) from VGS = -VGG.

- Intersection of load line with transfer characteristics will give Q point.

Fig 20 shows the position of Q point using the above procedure.

#### **JFET** parameters

**Transconductance:** The change in the Drain Current due to change in Gate to Source voltage is defined as Transconductance  $g_n$ .

C

Voltage is defined  $g_m = \frac{\Delta I_d}{\Delta V_{GS}}$ We know that,  $I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)$ And  $g_m = \frac{\Delta I_D}{\Delta V_{GS}}$ Differentiate Eq. (9) w.r.t V<sub>GS</sub>  $\frac{\Delta I_D}{\Delta V_{GS}} = I_{\text{DSS}} \times 2 \left( 1 - \frac{V_{GS}}{V_P} \right) \left( -\frac{1}{V_P} \right)$  $g_{\rm m} = -\frac{2I_{DSS}}{V_P} \left(1 - \frac{V_{GS}}{V_P}\right) - \dots (10)$ Also from Eq. (9)  $1 - \frac{V_{GS}}{V_P} = \sqrt{\frac{I_D}{I_{DSS}}} - \dots - (11)$ Therefore substitute Eq. (11) in Eq. (10), we get,  $g_m = -\frac{2I_{DSS}}{V_P} \sqrt{\frac{I_D}{I_{DSS}}} = -\frac{2}{V_P} \sqrt{\frac{I_D I_{DSS}^2}{I_{DSS}}}$ therefore  $g_m = -\frac{2}{V_P} \sqrt{I_D I_{DSS}}$  ----- (12) when  $V_{GS}=0$ ,  $g_m = g_{mo}$ therefore from Eq. (10),  $g_{mo} = -\frac{2I_{DSS}}{V_P}$  ----- (13) Substitute Eq. (13) in Eq. (10) we get,  $g_m = g_{mo} \left( 1 - \frac{V_{GS}}{V_P} \right)$

**Drain Resistance**,  $r_d$ : The ratio of change in Drain to Source voltage to change in Drain current is called Drain resistance,  $r_d$  with constant  $V_{GS}$ .

$$r_d = \frac{\Delta V_{DS}}{\Lambda I_{P}} \quad V_{GS=constant}$$

$r_d$  determines the output impedance  $Z_O$  of the JFET amplifier.

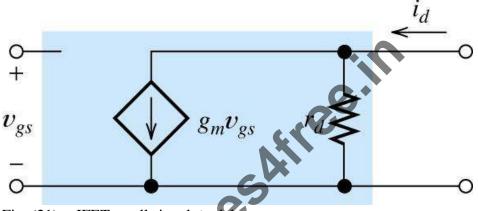

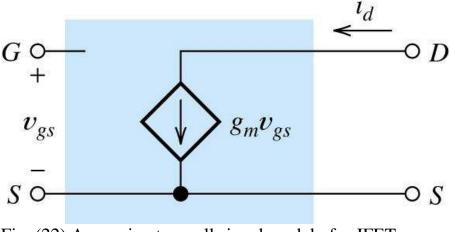

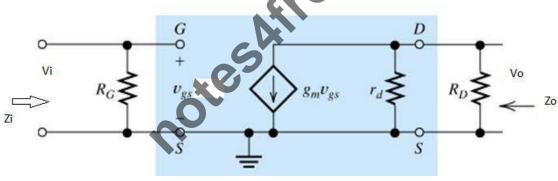

### JFET small signal model:

Fig. (21) shows low frequency small signal model for n-channel JFET. The relationship between  $I_D$  and  $V_{GS}\,$  is

$\Delta I_D = g_m \Delta V_{gs}$

and hence a current Source is connected from Drain to Source. The input impedance of JFET is high and hence  $I_G=0$ . Thus in the small signal model input impedance is representated by open circuit. The output impedance is representated by  $r_d$  from Drain to Source.

Fig. (21) n-JFET small signal model Approximate model

Since  $r_d$ >> external Drain resistance  $R_D$ ,  $r_d$  can be replaced by open circuit as shown in Fig. (22).

Fig. (22) Approximate small signal model of n-JFET.

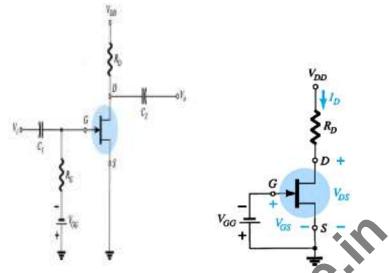

### COMMON SOURCE (CS) AMPLIFIER WITH FIXED BIASING:

Fig 23 shows CS amplifier with fixed bias RG is used to limit current in case VGG is connected with wrong polarity This would forward bias the gate-source junction causing high currents, which would destroy the transistor

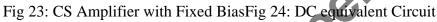

DC Analysis:

Open circuit C<sub>1</sub>& C<sub>2</sub> and current through RG i.e. IG=0. Therefore RG is represented by short circuits as shown in Fig. (24) Apply KVL to the input circuit of Fig. (24)  $V_{GG}$ - $V_{GS}$ =0  $V_{GS}$ =- $V_{GG}$  ----- (14) Since  $V_{GG}$  is constant,  $V_{GS}$  is fixed and hence the name fixed bias. Apply KVL to output circuit  $V_{DD}$ - $I_DR_D$ - $V_{DS}$ =0  $V_{DSQ}$ = $V_{DD}$ - $I_DR_D$  ----- (15) And  $I_D$  for fixed bias is  $I_{DQ}$ =  $I_{DSS} (1 - \frac{V_{GS}}{V_P})^2$ Therefore Q point is  $[V_{DS}, I_{DQ}]$

### Small signal analysis:

(i) To obtain AC equivalent circuit, short circuit  $C_1$ ,  $C_2$  and reduce DC voltages to zero.

(ii) Replace JFET by its small signal model to obtain AC equivalent circuit Fig. (25).

Fig 25: ac equivalent circuit

Z<sub>i</sub>: From the circuit, Fig. (25)

$Z_i = R_G$ Zo:

ree.1 Reduce  $V_i=0$ ,  $V_{gs}=0$  therefore  $g_mV_{gs}=0$ .  $Z_0 = R_D ||r_d|$ If  $r_d \gg R_D$ , Then  $Z_o = R_D$ Voltage gain, A<sub>V:</sub>  $A_{\rm V} = \frac{V_{ds}}{V_{gs}} = \frac{V_o}{V_i}$ From Fig. (25)  $V_o = -g_m V_{gs} (r_d || R_D)$  and  $A_{\rm V} = - g_m V_{\rm gs} \left( r_d \| R_{\rm D} \right)$ If  $r_d >> R_D$ ,  $A_V = -g_m R_D$ The negative sign indicates there is a phase shift of  $180^{\circ}$  between input and output voltages.

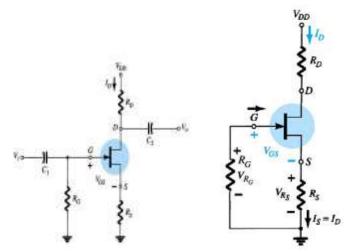

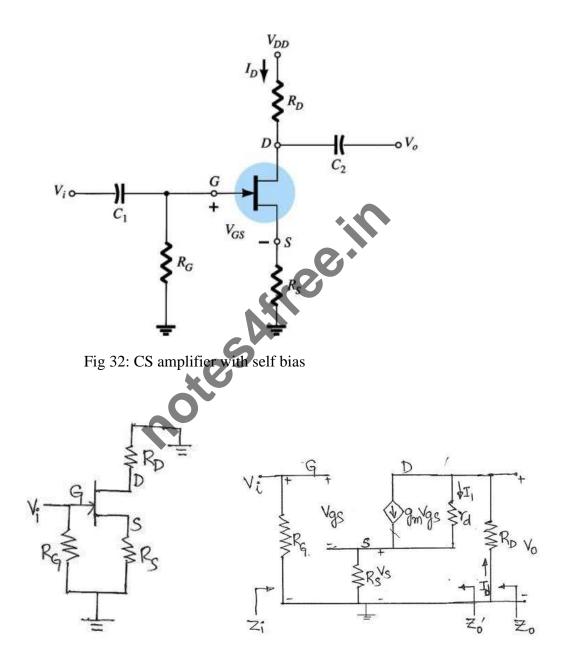

#### **COMMON SOURCE (CS) AMPLIFIER WITH SELF BIAS:**

Fig 26 shows Common Source amplifier with self bias. Voltage across RS determines gate to source voltage. Dc equivalent circuit is obtained by open circuiting all capacitors as shown in fig 27.

Apply KVL to Fig27,  $-V_{GS}-V_{S}=0$  $V_{S} = -V_{GS}$ . Also,  $V_S = I_D R_S$ Therefore,  $V_{GS} = -I_D R_S$ Apply KVL to output circuit of fig27,  $V_{DS} = V_{DD} - I_D R_S - I_D R_D$

Fig 26. CS amplifier with Self Bias

Fig 27 DC equivalent Circuit

Fig 28 : Q point

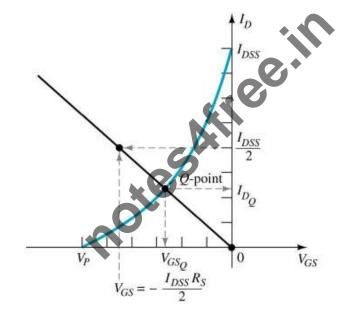

Fig 8 shows the location of Q point obtained by following procedure.

- Plot transfer characteristics

- Plot one point of load line at  $V_{GS} = 0$ ,  $I_D = 0$ .

- Second point can be obtained by choosing I<sub>D</sub> and finding V<sub>GS</sub>.

- $I_D = I_{DSS}/2$ , then

$V_{GS} = -I_D R_S = -I_{DSS}R_S/2$

Join two points to draw DC load line

• Intersection of load line with transfer characteristics will give Q point.

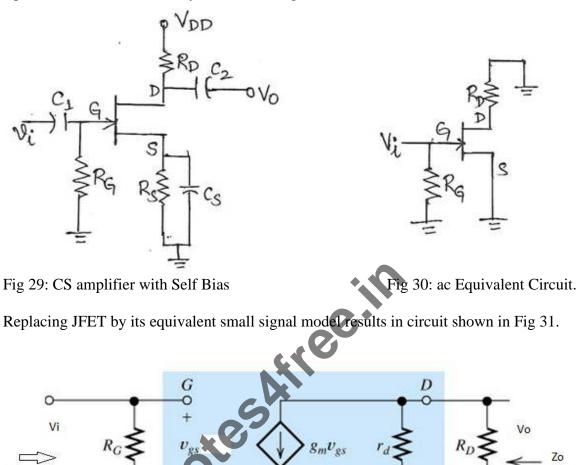

### CS amplifier with Self Bias(Bypassed Rs) -ac analysis

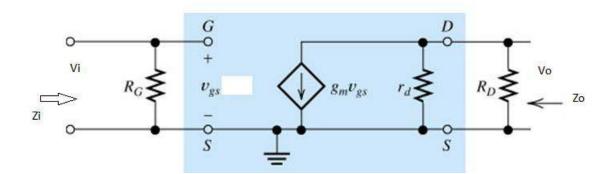

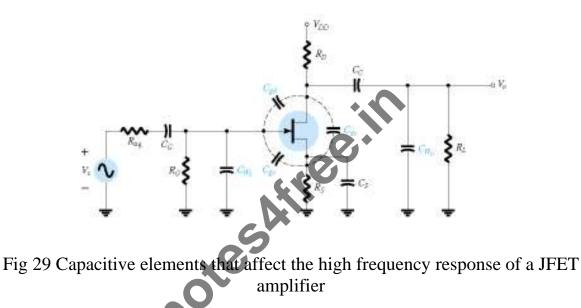

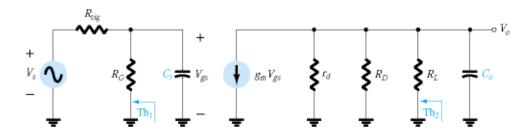

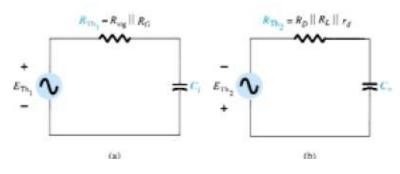

Fig 29 shows CS amplifier with Self bias and RS is bypassed by CS. Fig 30 shows ac equivalent Circuit obtained by short circuiting C1,C2,CS.

Fig 31: AC equivalent model of CS amplifier with Self bias

Z<sub>i</sub>: From the circuit, Fig. (31)  $Z_i = R_G$ Zo: Reduce  $V_i=0$ ,  $V_{gs}=0$  therefore  $g_mV_{gs}=0$ .  $Z_o = R_D ||r_d|$  $Ifr_d >> R_D$ , Then  $Z_o = R_D$ Voltage gain, Av:  $A_{\rm V} = \frac{V_{ds}}{V_{gs}} = \frac{V_o}{V_i}$ From Fig. (31)  $V_o = -g_m V_{gs} (r_d || R_D)$  and  $V_i = V_{gs}$  $A_{\rm V} = - g_{\rm m} V_{\rm gs} \left( r_{\rm d} \| R_{\rm D} \right)$ If  $r_d \gg R_D$ ,  $A_V = -g_m R_D$

The negative sign indicates there is a phase shift of 180<sup>0</sup> between input and output voltages.

### CS amplifier with Self Bias(UnBypassedRs) -ac analysis

Fig 32 shows CS amplifier with self bias but RS is unbypassed. To obtain ac equivalent circuit, c1 and c2 are short circuited as shown in Fig33. Replacing JFET by its equivalent small signal model, we get the circuit shown in fig 34.

Fig 33: ac Equivalent Circuit

Fig 34: ac Equivalent model

Zi: From Fig 34,  $Z_i = R_G$ .

Zo': Output impedance excluding RD.  $Z_o' = V_o/I_d$ Apply KVL to the output circuit of Fig 34,  $V_o = I_1 r_d + I_d R_S$ But,  $I_1 = I_d - g_m V_{gs}$ . Therefore,  $V_0 = (I_d - g_m V_{gs}) + I_d R_s$ -----(16) Apply KVL to the input circuit of Fig 34,  $V_i - V_{gs} - I_d R_s = 0$  $V_{gs} = -I_d R_S + V_i$ For output impedance,  $V_i = 0$ . Therefore,  $V_{gs} = -I_d R_S$ -----(17) Substituting Eq (17) in (16) $V_0 = I_d(r_d + g_m R_S r_d + R_S)$ Therefore,  $Z_o' = V_o/I_d = r_d + g_m R_s r_d + R_s$ But,  $\mu = g_m r_d$ Therefore,  $Z_0' = r_d + R_s(\mu + 1)$ -----(18) Thus, output impedance with unbypassed RS is increased. (19) Zo: Output impedance considering RD  $Zo = Z_0' ||R_D$ Voltage Gain ,AV: From Fig 34,  $V_o = -I_d R_D$ ------Apply KVL to the outer part of Fig 34,  $(I_d - g_m V_{gs})r_d + I_d R_D + I_d R_S = 0;$ ------(20)Also  $V_{gs} = V_i - I_d R_s$ ------Eq (21) in Eq (20)  $I_d = (g_m V_i r_d) / (r_d + g_m R_S r_d + R_s \pm$ R<sub>D</sub>) -(22) Eq (22) in Eq (19)  $V_o = (-g_m V_i r_d R_D) / (r_d + g_m R_S r_d + R_S + R_D)$  $A_{\rm V} = V_{\rm o}/V_{\rm i} = -g_{\rm m}r_{\rm d}R_{\rm D}/r_{\rm d} + g_{\rm m}R_{\rm S}r_{\rm d} + R_{\rm S} + R_{\rm D}$ If  $r_d \gg R_S + R_D$ ,  $A_{\rm V} = -g_{\rm m}R_{\rm D}/(1+g_{\rm m}R_{\rm S})$

Example: For the CS amplifier shown, operating point is defined by  $V_{GSQ} = -2.5V$ ,  $V_P = -6V$  and  $I_{DQ} = 2.5mA$  with  $I_{DSS} = 8mA$ .Calculate  $g_m$ ,  $r_d$ , $Z_i$ , $Z_o$  and  $A_V$ . Take Yos =  $20\mu S$

(i)

$$g_m = g_{mo} \left( 1 - \frac{V_{GS}}{V_P} \right)$$

$$\begin{split} g_{mo} &= -\frac{2I_{DSS}}{V_P} = \frac{2 \times 8 \times 10^{-3}}{6} = 2.67 mS \\ g_m &= g_{mo} \left( 1 - \frac{V_{GS}}{V_P} \right) = \left( 1 - \frac{(-2.5V)}{(-6v)} \right) = 1.58 mS \\ (ii) \quad r_d &= \frac{1}{Y_{OS}} = \frac{1}{20 \times 10^{-6}} = 50 K\Omega \\ (iii) \quad Z_i &= R_G = 1 M\Omega \\ (iv) \quad Z_o &= Z_0' ||R_D = r_d + R_S(\mu +)||RD = 2163.41\Omega \\ (v) \end{split}$$

$$A_{\rm V} = \frac{V_o}{V_i} = -g_{\rm m}r_{\rm d}R_{\rm D}/r_{\rm d} + g_{\rm m}R_{\rm S}r_{\rm d} + R_{\rm S} + R_{\rm D} = -1.315.$$

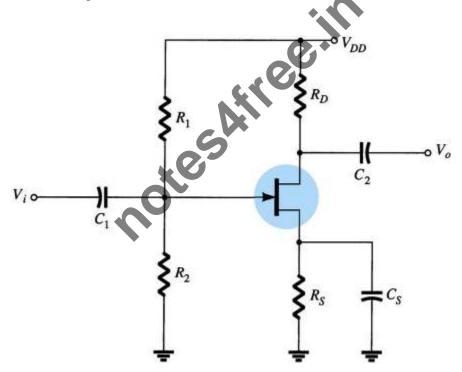

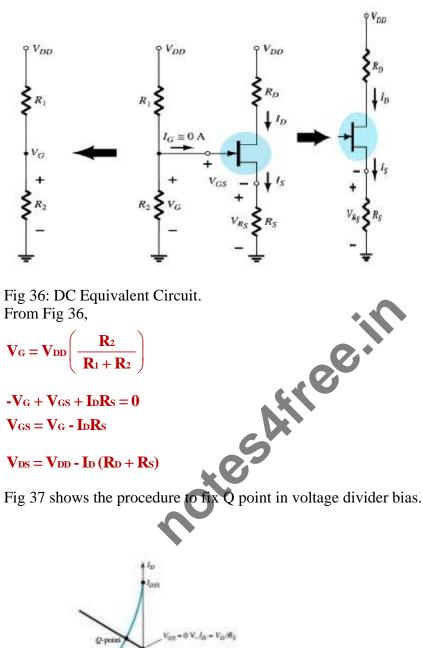

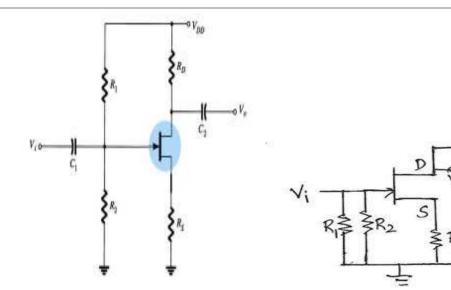

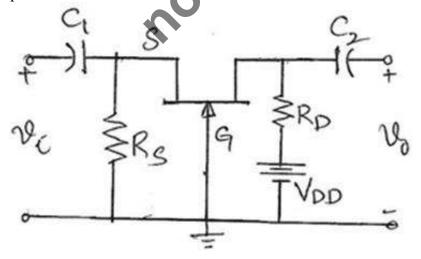

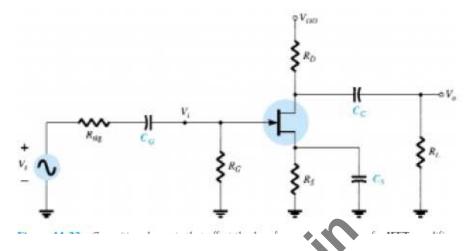

# CS amplifier with Voltage Divider Bias(Bypassed Rs):

Fig 35 Shows voltage divider bias circuit.

Fig 35: Voltage Divider Bias

DC analysis: Open circuit C1, C2, CS and the resultant circuit is as shown in Fig 36.

Fig 37: Fixing Q Point.

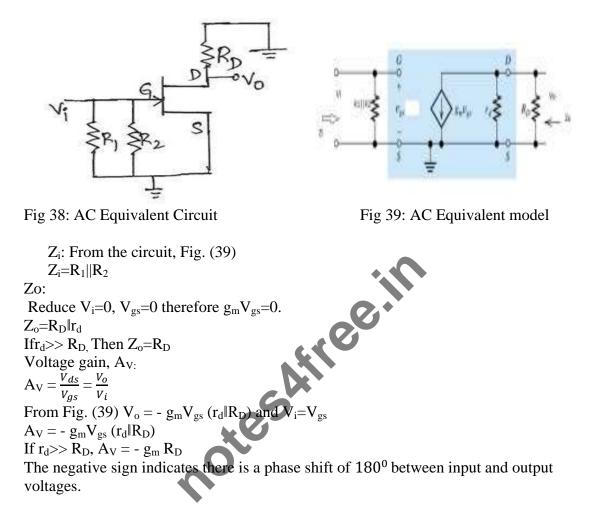

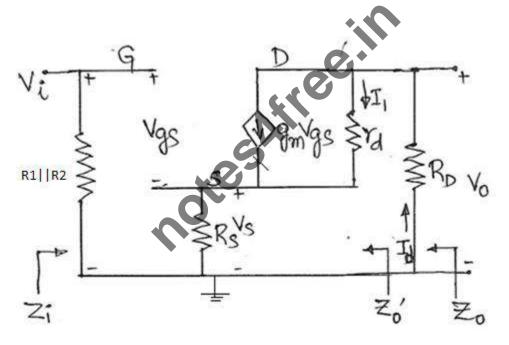

AC Analysis: AC Equivalent Circuit is obtained by Shorting C1, C2 and CS as shown in Fig 38. Replacing JFET by its small signal model, we get the circuit shown in Fig 39.

### CS amplifier with Voltage Divider Bias (UnBypassed Rs): ac Analysis

Fig 40 Shows CS voltage divider bias with un-bypassed RS. AC Analysis is obtained by short circuiting C1,C2 and the resultant circuit is shown in Fig 41. Replacing JFET by its equivalent small signal model, we get circuit shown in Fig 42.

RD

Fig 40: CS amplifier with Voltage Diver Bias

Fig 41: Ac Equivalent Circuit

Fig 42: AC equivalent Model

Zi: From Fig 42,  $Z_i = R_1 || R_2$ . Zo': Output impedance excluding RD.  $Z_o' = V_o/I_d$ Apply KVL to the output circuit of Fig 42,  $V_o = I_1 r_d + I_d R_S$ But,  $I_1 = I_d - g_m V_{gs}$ . Therefore,  $V_o = (I_d - g_m V_{gs}) + I_d R_S$ ------(23) Apply KVL to the input circuit of Fig 42,  $V_i - V_{gs} - I_d R_S = 0$

$V_{gs} = -I_d R_S + V_i$ For output impedance,  $V_i = 0$ . Therefeore,  $V_{gs} = -I_d R_S$ ------(24) Substituting Eq (24) in (23)  $V_0 = I_d(r_d + g_m R_S r_d + R_S)$ Therefore,  $Z_o' = V_o/I_d = r_d + g_m R_s r_d + R_s$ But,  $\mu = g_m r_d$ Therefore,  $Z_0' = r_d + R_s(\mu + 1)$ -----(25) Thus, output impedance with unbypassed RS is increased. Zo: Output impedance considering RD  $Zo = Z_0' || R_D$ Voltage Gain ,AV: From Fig 42,  $V_0 = -I_d R_D$ -----(26) Apply KVL to the outer part of Fig 42,  $(I_d - g_m V_{gs})r_d + I_d R_D + I_d R_S = 0;$ -----(27) Also  $V_{gs} = V_i - I_d R_s$ -----(28) Eq (27) in Eq (26)  $I_{d} = (g_{m}V_{i}r_{d})/(r_{d} + g_{m}R_{S}r_{d} + R_{s} + R_{D})$ -----(29) Eq (22) in Eq (19)  $V_{o} = (-g_{m}V_{i}r_{d}R_{D})/(r_{d} + g_{m}R_{S}r_{d} + R_{S} + R_{D})$  $A_V = V_o/V_i = -g_m r_d R_D/r_d + g_m R_S r_d + R_S + R_D$ If  $r_d \gg R_S + R_D$ ,  $A_{\rm V} = -g_{\rm m}R_{\rm D}/(1+g_{\rm m}R_{\rm S})$

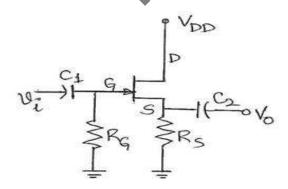

# Common Drain (CD)/ Source Follower Configuration:

Fig. (43) shows Common Drain configuration. The input is applied between Gate and Source and output between Source and Ground (i.e. Drain is grounded during AC analysis)

Fig 43: Source Follower Circuit

From the circuit in Fig 43,

$V_{\rm G} + V_{\rm GS} - V_{\rm S} = 0$

Therefore  $V_G + V_{GS} = V_S$

When a signal is applied to JFET gate via  $C_1$ ,  $V_G$  varies with the signal. As  $V_{GS}$  is constant and  $V_S = V_G + V_{GS}$  varies with  $V_i$ . As the output voltage at the Source ( $V_S$ )

follows changes in the signal voltage applied to the gate, this circuit is also called Source follower.

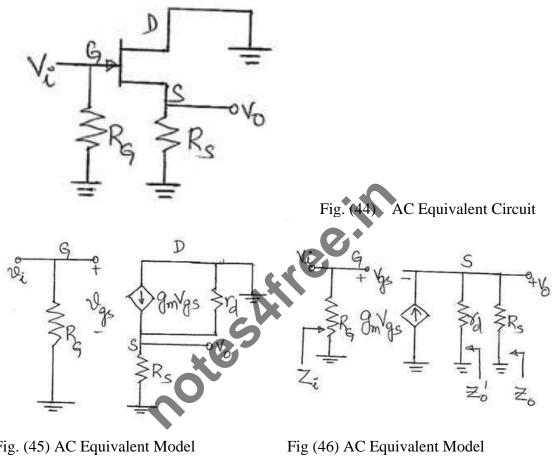

The AC equivalent circuit and low frequency equivalent model for Source follower is as shown in Fig. (44) and Fig. (45) respectively.

Fig. (45) AC Equivalent Model  $V_i - V_{gs} - V_o = 0$ V<sub>o</sub>=V<sub>i</sub>-V<sub>gs</sub>  $V_o + V_{gs} - V_i = 0$ V<sub>gs</sub>=V<sub>i</sub>-V<sub>o</sub>  $V_i = 0, V_{gs} = -V_o$ Z<sub>i</sub>: From the input circuit,  $Z_i = R_G$ **Output Z:Z**<sub>o</sub> Fig. (45) can also be written as Fig. (46)  $\hat{Z}_0 = \frac{V_0}{I_d}$ Apply KVL to the output loop of Fig 46,  $V_i - V_{gs} - V_o = 0$ For  $Z_o$ ,  $V_i=0$ ,  $V_o=V_{gs}$ But from Fig. (46),  $I_d = g_m V_{gs}$

Therefore  $g_m V_o = I_d$  $\vec{Z}_O = \frac{V_O}{I_d} = \frac{1}{g_m}$ Therefore  $Z_0 = Z_0 \| R_S$  $\mathbf{Z}_{\mathrm{o}} = \frac{1}{g_m} \parallel \mathbf{R}_{\mathrm{S}}$ Voltage Gain, Av  $A_{\rm V} = \frac{\breve{V}_o}{V_i}$ From Fig. (46),  $V_o = I_d (r_d \| R_S)$ And  $I_d = g_m V_{gs}$ Therefore  $V_o = g_m V_{gs} (r_d || R_S)$ From input circuit  $V_i = -V_{gs} + V_o$ Therefore  $V_i = -g_m V_{gs} (r_d \parallel R_S) - V_{gs}$ Therefore  $A_V = \frac{V_o}{V_i} = \frac{-g_m V_{gs} (r_d \parallel R_S)}{-V_{gs} [g_m (r_d \parallel R_S) + 1]}$ e.Ir  $A_{V} = \frac{g_{m}(r_{d} \parallel R_{S})}{1 + [g_{m}(r_{d} \parallel R_{S})]}$ If  $rd \gg RS$ ;  $\mathbf{r}_{d} \parallel \mathbf{R}_{S} \approx \mathbf{R}_{S}$  $A_{\rm V} = \frac{g_m R_S}{1 + g_m R_S}$ If  $g_m R_s >> 1$ ,  $A_V \approx 1$  but it is always less than one. There is no phase shift between input and output voltages. Source Follower exhibits following Characteristics;

- High input Impedance.

- Low Output Impedance

- Voltage gain is less than 1.

- No phase shift between input and output.

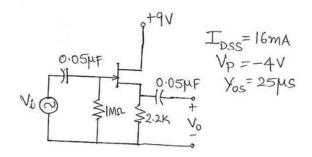

Example: A DC analysis of Source Follower network shown in Fig. below results in  $V_{GSQ}$ = -2.86V and  $I_{DQ}$ =4.56mA. Determine (i)  $g_m$  (ii)  $r_d$  (iii)  $Z_i$  (iv)  $Z_o$  with and without  $r_d$  (v)  $A_V$  with and without  $r_d$ . Take  $I_{DSS}$ =16mA,  $V_P$ =-4V,  $Y_{OS}$ =25 $\mu$ S.

(i)

$$g_{mo} = \frac{2I_{DSS}}{V_P} = \frac{2 \times 16 \times 10^{-3}}{4} = 8 \text{mS}$$

$g_m = g_{mo} \left(1 - \frac{V_{GSQ}}{V_P}\right) = 8 \times 10^{-3} \left(1 - \frac{(-2.86)}{(-4)}\right)$

$g_m = 2.28 \times 10^{-3} \text{ S.}$

(ii)  $r_d = \frac{1}{Y_{OS}} = \frac{1}{25 \times 10^{-6}} = 40 \text{K}\Omega$

(iii)  $Z_i = R_G = 1 \text{M}\Omega$

(iv) With  $r_d$

$Z_o = r_d \| R_S \| \frac{1}{g_m} = 40 \text{K} \| 2.2 \text{K} \| \frac{1}{2.28 \times 10^{-3}}$

$= 362.52 \Omega$

Without  $r_d$

$Z_o = R_S \| \frac{1}{g_m} = 2.2 \times 10^3 \| \frac{1}{2.28 \times 10^{-3}}$

$= 365.69 \Omega$

(v)  $A_V$  With  $r_d$

$A_V = \frac{g_m (r_d \| R_S)}{1 + [g_m (r_d \| R_S)]} = 0.826.$

$A_V$  Without  $r_d$

$A_V = \frac{g_m R_S}{1 + g_m R_S} = \frac{2.28 \times 10^{-3} \times 2.2 \times 10^3}{1 + 2.28 \times 10^{-3} \times 2.2 \times 10^3} = 0.833$

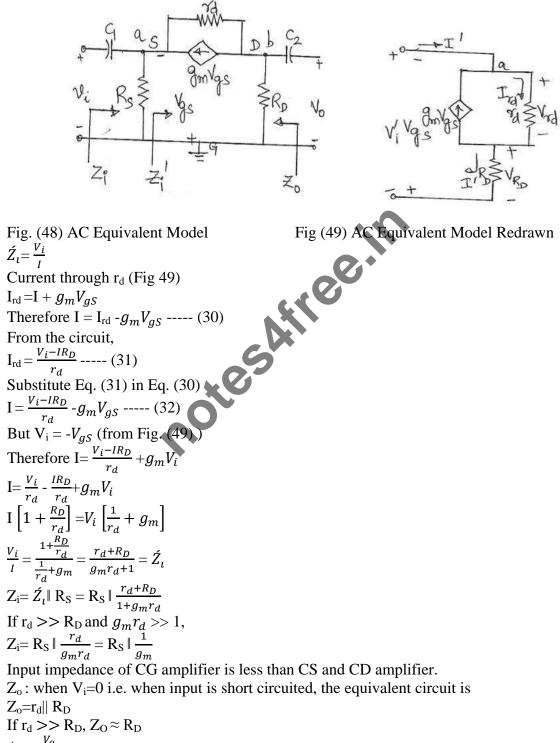

# Common Gate (CG) Configuration:

Fig. (47) shows CG configuration, the input is applied between Source and Gate and output is taken between Drain and Gate.

Fig. (47) Common Gate Configuration

In CG configuration, Gate voltage is constant. An increase in  $V_i$  in positive direction increases the -Ve Gate to Source bias voltages. Due to this Drain current reduces, reducing the drop  $I_DR_D$ . Since  $V_D = V_{DD}$ -  $I_DR_D$ , the reduction in  $I_D$  results in an

increase in output  $V_g V_D$ . Similarly when input  $V_g$  reduces, opposite action takes place which reduces the output voltage. Thus there is no phase shift between input and output in a Common Gate amplifier. AC equivalent model of CG amplifier is as shown in Fig. (48).

$V_{O}=-I_{D}R_{D} \text{ and } V_{i}=-V_{gs}$ Apply KVL to Fig. (b) outer loop  $V_{i}+(I_{d}-g_{m}V_{gs})r_{d}+I_{D}R_{D}=0$ But  $V_{gs}=-V_{i}$ Therefore Vi +  $I_{d}R_{d}+g_{m}V_{i}r_{d}+I_{D}R_{D}=0$ Vi [1+ $g_{m}r_{d}$ ] +  $I_{d}$  [ $r_{d}+R_{D}$ ] =0

- $I_{d}$  [ $r_{d}+R_{D}$ ] = Vi [1+ $g_{m}r_{d}$ ]  $V_{i}=\frac{-I_{d}(r_{d}+R_{D})}{1+g_{m}r_{d}}$ Av =  $\frac{V_{o}}{V_{i}}=\frac{R_{D}(1+g_{m}r_{d})}{r_{d}+R_{D}}$ If  $r_{d} >> R_{D}, g_{m}r_{d} >> 1$ Av =  $\frac{R_{D}(g_{m}r_{d})}{r_{d}}=R_{D} g_{m}$

Thus there is no phase shift between input and output in CG amplifier.

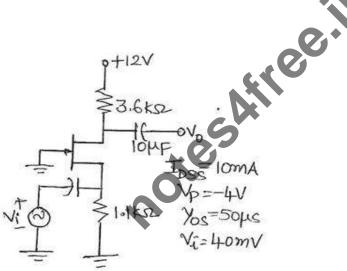

Example: For the network shown , if  $V_{GSQ} = -2.2V$  and  $I_{DQ} = 2.03$ mA. Determine  $g_m, r_d$ . Calculate  $Z_i$  with and without  $r_d$ ,  $Z_o$  with and without  $r_d$ . Determine  $v_o$  with and without  $r_d$ .

(i)

$$g_{mo} = \frac{2I_{DSS}}{V_P} = \frac{2 \times 10 \times 10^{-3}}{4} = 5 \text{mS}$$

$g_m = g_{mo} \left( 1 - \frac{V_{GSQ}}{V_P} \right) = 5 \times 10^{-3} \left( 1 - \frac{(-2.2)}{(-4)} \right)$

$g_m = 2.25 \times 10^{-3} \text{ S.}$

(ii)

$$r_d = \frac{1}{Y_{OS}} = \frac{1}{50 \times 10^{-6}} = 20 K\Omega$$

(iii)

$$\frac{r_d + R_D}{g_m r_d + 1} = \dot{Z}_l = 0.31 \text{K}\Omega$$

(iv)

$$Z_i = \hat{Z}_i \| R_S = R_S \| \frac{r_d + R_D}{1 + g_m r_d} = 0.35 K\Omega$$

(v)

$$Z_{O} \approx R_{D} = 3.6 K \Omega$$

$$_{(vi)} \qquad Z_o = r_d || R_D = 3.05 K \Omega$$

(vii)  $A_{\rm V} = R_{\rm D} g_m = 8.1$

(viii)

$$A_V = \frac{V_o}{V_i} = \frac{R_D(1+g_m r_d)}{r_d + R_D} = 7.02$$

(ix) vo without rd = 324mV

vo = 280.8mV

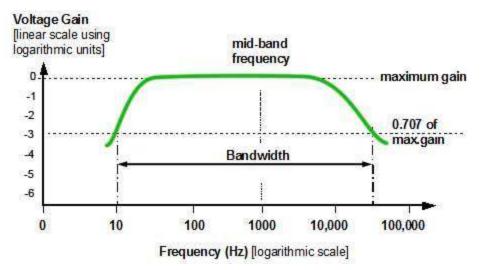

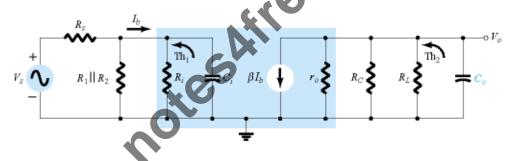

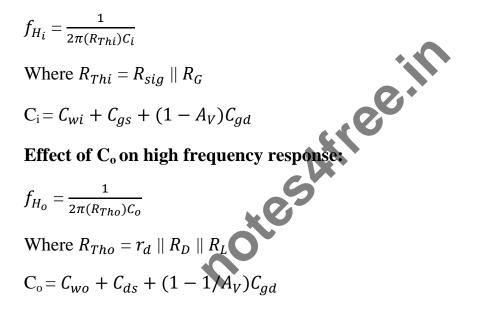

### **Module 3: TRANSISTOR and FET FREQUENCY RESPONSE**

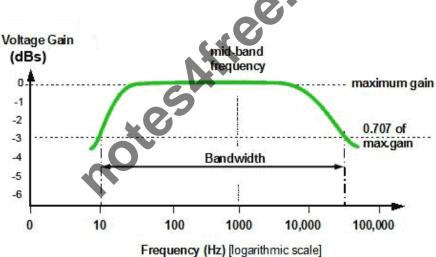

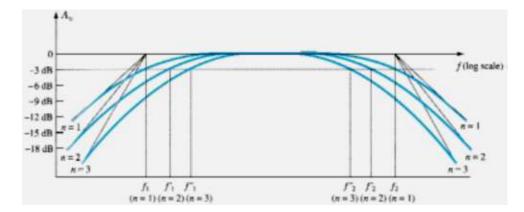

The frequency response of an amplifier is the plot of the magnitude of voltage gain as a function of frequency. In transistor amplifier the low frequency response is governed by coupling and bypass capacitors. The high frequency response is affected by the transistor parasitic capacitances and stray wiring capacitances. The mid frequency response is unaffected by these capacitances.

### General frequency considerations:

The response of a single stage or multistage amplifier depends on the frequency of the applied signal. The coupling and bypass capacitors affect the low frequency response since the reactance of these capacitors decreases with increase in frequency. The internal capacitances of the active devices and the stray wiring capacitances will limit the high frequency response of the system. An increase in the number of stages of a cascaded system will also limit the low and high frequency responses.

# Frequency response of RC Coupled amplifier:

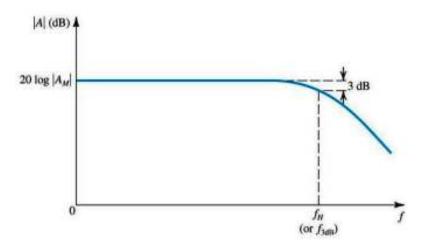

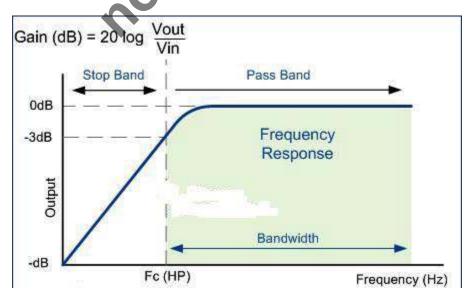

Fig. (1) shows the frequency response of RC coupled amplifier. The horizontal scale is a logarithmic scale to permit a plot extending from low to high frequency regions. The frequency range is divided into 3 regions.

- (i) Low frequency region.

- (ii) Mid frequency region.

- (iii) High frequency region.

The drop in the gain at low frequencies is due to the coupling capacitors ( $C_C$ , $C_S$ ) and bypass capacitors ( $C_E$ ). At high frequencies the drop in gain is due to the internal device capacitances and the stray wiring capacitances. In the mid frequency range the gain is almost independent of the frequency. This is due to the fact that at mid frequencies the coupling and bypass capacitors act as short circuits and the device and stray wiring capacitances act as open circuits due to their low capacitance. The mid band gain is denoted as  $Av_{mid}$ .

Fig. (1) Frequency response of RC coupled amplifier.

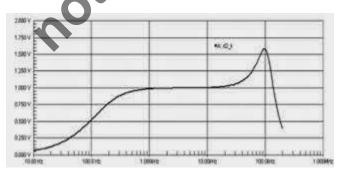

### Frequency response of transformer coupled amplifier:

Fig.(2) shows frequency response of transformer coupled amplifier. The magnetizing inductive reactance of the transformer winding is  $X_L=2\pi fl$ . At low frequencies the gain drops due to small value of  $X_L$ . At f=0 (DC) there is no change in flux in the core. As a result the secondary induced voltage or output voltage is zero and hence the gain. At high frequencies the gain drops due to stray capacitance between the turns of primary and secondary windings.

Fig. (2) Frequency response of transformer coupled amplifier.

## Frequency response of direct coupled amplifier:

Fig. (3) shows frequency response of direct coupled amplifier. Since there are no coupling or bypass capacitors, there is no drop in gain at low frequencies. It has a flat response to the upper cut-off frequency. Gain drops at high frequencies due to device internal capacitances and the stray wiring capacitances.

Fig. (3) Frequency response of direct coupled amplifier.

### Half power frequencies and bandwidth:

The frequencies  $f_1$  and  $f_2$  at which the gain is 0.707 Av<sub>mid</sub> are called cut-off frequencies or corner frequencies or break frequencies.  $f_1$  is called the lower cut-off frequency and  $f_2$  is called the upper cut-off frequency.

Bandwidth or pass band of the amplifier is

$BW = f_2 - f_1 - \dots + (1)$

The output voltage in the mid band is  $|V_0| = |Av_{mid}| |V_i|$

Output power in the mid band is

$$P_{O(mid)} = \frac{|V_O|^2}{R_O} = \frac{|Av_{mid}|^2 |V_i|^2}{R_O} - \dots (2)$$

The output voltage at cut-off frequencies is

$$|V_0| = |0.707 \text{Av}_{mid}| |V_i|$$

The output power at cut-off frequencies is

$$P_{O (cut-off)} = \frac{|0.707 A v_{mid}|^2 |V_i|^2}{R_0}$$

$$= \frac{0.5 |Av_{mid}|^2 |V_i|^2}{R_0}$$

$$= 0.5 P_{O \text{(mid)}} ----- (3)$$

Thus, the output power at cut-off frequencies is half the mid band power output.  $f_1$  is called the lower half power frequency and  $f_2$  is called the upper half power frequency.

### Normalized gain V/s Frequency plot:

The normalized gain is obtained by dividing the gain Av at each frequency by the mid band gain  $Av_{mid}$ .

Fig. (4) Normalized gain V/s frequency plot

Normalized decibel gain is  $\frac{A_V}{Av_{mid}}\Big|_{dB} = 20 \log_{10} \left[\frac{A_V}{Av_{mid}}\right]$ -----(5)

Normalized decibel voltage gain in mid band is

$$20 \log_{10} \left[ \frac{A_V}{Av_{mid}} \right] = 0$$

Normalized decibel voltage gain at cut-off frequencies is

$$20\log_{10}\left[\frac{0.707A_V}{Av_{mid}}\right] = -3\mathrm{dB}$$

Since normalized decibel voltage gain at cut-off frequencies is 3dB less than the normalized decibel mid band voltage gain.  $f_1$  and  $f_2$  are also called 3dB frequencies.

- $f_1 \rightarrow \text{lower 3dB frequency}$

- $f_2 \rightarrow upper 3dB$  frequency

Fig. (5) shows the plot of normalized dB voltage gain V/s frequency for an RC coupled amplifier.

Fig. (5) Plot of normalized decibel voltage gain V/s frequency.

### Phase angle plot:

A single stage RC coupled amplifier introduces a  $180^{\circ}$  phase shift between input and output signals in the mid band region. At low frequencies the output voltage  $V_0$  lags  $V_i$  by an additional angle  $\theta_1$ . Therefore, the total phase phase shift between  $V_0$  and  $V_i$  is more than  $180^{\circ}$ . At high frequencies,  $V_0$  leads  $V_i$  by an additional angle  $\theta_2$ . As a result, the total phase shift drops below  $180^{\circ}$ . Fig. (6) shows the phase plot for a single stage RC coupled amplifier.

Fig. (6) Phase plot of single stage RC coupled amplifier.

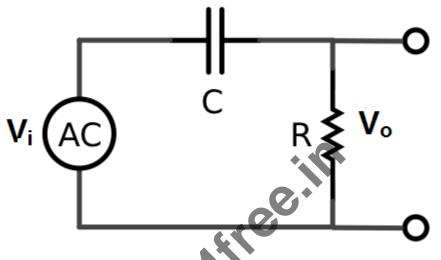

### Low frequency analysis:

In the low frequency region of a single stage BJT amplifier, the amplifier gain increases with frequency. Hence it can be modelled as a high pass RC circuit as shown in Fig. (7).

Fig. (7) Amplifier modelled as high pass RC circuit.

The capacitor C represents the combined effect of coupling and bypass capacitors and the resistance R represents the combined effect of resistive elements of the amplifier network.

The capacitive reactance is

$$X_{\rm C} = \frac{1}{2\pi fc} \dots (6)$$

At f=0,  $X_C = \infty \Omega$ . i.e. at low frequencies, the capacitor acts as a open circuit as shown in Fig. (8)

From Fig. (8), V<sub>0</sub>=0.

Fig. (8) at f=0

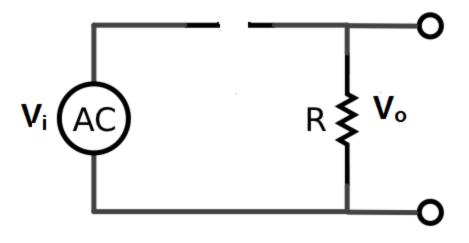

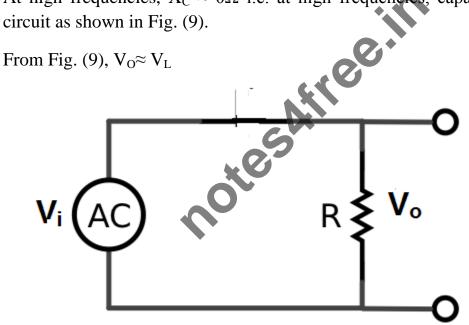

At high frequencies,  $X_C\approx 0\Omega$  i.e. at high frequencies, capacitor acts as a short circuit as shown in Fig. (9).

Fig. (9) at high frequencies

Hence as the input signal frequency increases from zero to mid band value, the output voltage rises from zero to  $V_{i}$  and hence the gain from zero to 1.

### Mathematical analysis:

Apply Voltage division rule to circuit in Fig. (7),

$$\mathbf{V}_{\mathrm{O}} = \frac{V_i R}{R - j X_C}$$

Voltage gain is given by

$$A_{V} = \frac{V_{o}}{V_{i}} = \frac{R}{R - jX_{C}} = \frac{R}{R[1 - j\frac{X_{C}}{R}]}$$

$$A_{V} = \frac{1}{1 - j[\frac{X_{C}}{R}]} - \dots (7)$$

The magnitude of voltage gain is

$$|A_{V}| = \frac{1}{\sqrt{1 + [\frac{X_{C}}{R}]^{2}}} - .... (8)$$

(i) At f=0,  $X_{C} = \frac{1}{2\pi fc} = \infty \Omega$  therefore  $|A_{V}| = 0$

(ii) At high frequencies,  $f \rightarrow \infty$ , therefore  $X_{C} \rightarrow 0$ . Hence  $|A_{V}| \rightarrow 1 = |A_{V}|_{mid}$

$|A_{V}|_{mid (dB)} = 20 \log_{10}(1) = 0 dB$

(iii) When  $X_{C} = R - .... (9)$

$|A_{V}| = \frac{1}{\sqrt{2}} \Rightarrow \frac{V_{0}}{V_{i}} = \frac{1}{\sqrt{2}}$  or  $V_{0} = 0.707 V_{i}$

The corresponding decibel gain is

$$20 \log_{10} \frac{1}{\sqrt{2}} = -3 \mathrm{dB}$$

From Eq. (9),  $\frac{1}{2\pi fc} = R$

$$f = \frac{1}{2\pi Rc}$$

The frequency given by the above Eq. is the lower cut-off frequency or lower 3dB cut-off frequency denoted by  $f_1$ .

Therefore

$$f_1 = \frac{1}{2\pi Rc} - \dots - (10)$$

$$\frac{X_C}{R} = \frac{1}{2\pi f c R} = \left[\frac{1}{2\pi R c}\right] \times \frac{1}{f} = \frac{f_1}{f}$$

Using in Eq. (7) and (8)

$$A_{V} = \frac{1}{1 - j[\frac{f_{1}}{f}]} - \dots + (11)$$

$$|A_{V}| = \frac{1}{\sqrt{1 + [\frac{f_{1}}{f}]^{2}}} - \dots + (12)$$

From Eq. (11), phase angle of  $A_V$  is

$$\theta_1 = \tan^{-1} \left[ \frac{f_1}{f} \right] \dots \dots (13)$$

Since  $\theta_1$  is +Ve, V<sub>0</sub> leads V<sub>i</sub> by an angle  $\theta_1$

In magnitude and phase form, Eq. (11) can be written as Arre

$$A_{\rm V} = |A_{\rm V}| \Delta \theta_1$$

=  $\frac{1}{\sqrt{1 + [\frac{f_1}{f}]^2}} \Delta \tan^{-1} \left[\frac{f_1}{f}\right] - \dots (14)$

Fig. (10) shows the plot of A V/s frequency.

Fig. (10) Low frequency response of high pass RC circuit.

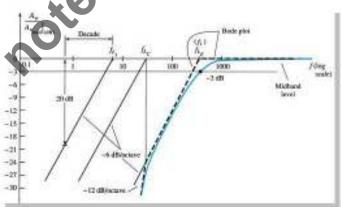

### **Bode plot of low frequency response:**

From Eq. (12), we have

$$|\mathbf{A}_{\mathbf{V}}| = \frac{1}{\sqrt{1 + [\frac{f_1}{f}]^2}}$$

Voltage gain in dB is

$$|A_{\rm V}|_{\rm dB} = 20 \log_{10} \left[ \frac{1}{\sqrt{1 + [\frac{f_1}{f}]^2}} \right]$$

$$|A_{\rm V}|_{\rm dB} = -20 \log_{10} \sqrt{1 + [\frac{f_1}{f}]^2} -\dots (15)$$

To construct the plot of  $|A_V|_{dB} V/s$  frequency using straight line segments, we consider the following frequency ranges. (a) For frequencies  $f \ll f_1$  or  $\frac{f_1}{f} \gg 1$ Eq. (15) can be approximated as

$$|A_{\rm V}|_{\rm dB} = -20 \log_{10} \sqrt{[\frac{f_1}{f}]^2}$$

$$|\mathbf{A}_{\mathbf{V}}|_{\mathbf{dB}} = -20 \log_{10} \left[\frac{f_1}{f}\right] \dots (16)$$

$|A_V|_{dB}$  is calculated at different values of  $\frac{f_1}{f}$  and tabulated in table (1).

| f                | $\frac{f_1}{f}$ | $ A_{\rm V} _{\rm dB} = -20 \log_{10} \left[\frac{f_1}{f}\right]$ |

|------------------|-----------------|-------------------------------------------------------------------|

| $\frac{f_1}{10}$ | 10              | -20dB                                                             |

| $\frac{f_1}{4}$  | 4               | -12dB                                                             |

| $\frac{f_1}{2}$ | 2 | -6dB |

|-----------------|---|------|

| $f_1$           | 1 | 0dB  |

Table (1):  $|A_V|_{dB}$  at different frequencies.

Following conclusions can be drawn from table (1).

- (i) A change in frequency by a factor of 2 is equal to one octave. When the frequency changes from  $\frac{f_1}{4}$  to  $\frac{f_1}{2}$  or  $\frac{f_1}{2}$  to  $f_1$  (one octave), the gain increases by 6dB.

- (ii) A change in frequency by a factor of ten is equal to one decade. When the frequency changes from  $\frac{f_1}{10}$  to  $f_1$  (one decade), the gain increases by 20dB.

- (iii) If a plot of  $|A_V|_{dB}$  against log scale in the frequency range  $\frac{f_1}{10} < f < f_1$  is plotted, a straight line with slope 6dB/octave or 20dB/decade is obtained as shown in Fig. (11).

Fig. 11: Bode plot for low frequency region.

(b) For frequencies,  $f >> f_1$  or  $\frac{f_1}{f} <<1$ Eq. (15) can be approximated by

$|A_V|_{dB} \approx$  - 20  $log_{10}$  1=0dB.

The plot of  $|A_V|_{dB}$  against log scale for the frequency range  $f \gg f_1$ , is a straight line on the frequency axis as shown in Fig. (11). The slope of this line is zero, since the gain is constant at 0dB. The plot in Fig. (11) is made of 2 straight line segments called asymptotes with a break point at  $f_1$ . Hence  $f_1$  is called break frequency or corner frequency. This peicewise linear plot is also called bode magnitude plot or simply bode plot.

From bode plot, at  $f = f_1$ ,  $|A_V|_{dB} = 0$ .

From bode plot, at  $f = f_1$ ,  $|A_V|_{dB} = -3$ .

Thus, at  $f = f_1$ , the gain read from bode plot differs from the actual gain by 3dB.

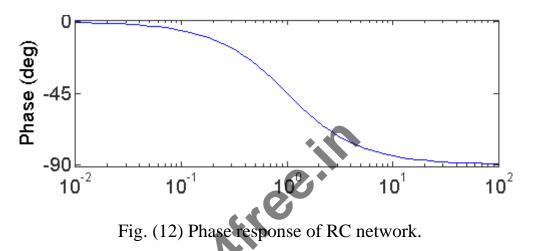

## **Phase Plot:**

At low frequencies,  $V_0$  leads  $V_i$  by an angle  $\theta_1$  given by

$$\theta_1 = \tan^{-1} \left[ \frac{f_1}{f} \right] \dots \dots (17)$$

41ee The value of  $\theta_1$  is calculated at different values of  $\frac{f_1}{f}$  as shown in table (2).

| f                         | $\frac{f_1}{f}$ | $\theta_1 = \tan^{-1} \left[ \frac{f_1}{f} \right]$ | Total phase shift<br>$\theta = 180 + \theta_1$ |

|---------------------------|-----------------|-----------------------------------------------------|------------------------------------------------|

| 0                         | x               | 90 <sup>0</sup>                                     | $270^{0}$                                      |

| $\frac{f_1}{100}$         | 100             | 89.4 <sup>0</sup>                                   | 269.4 <sup>0</sup>                             |

| $f_1$                     | 1               | $45^{0}$                                            | 225 <sup>0</sup>                               |

| 100 <i>f</i> <sub>1</sub> | 0.01            | $0.572^{0}$                                         | $180.572^{\circ}$                              |

| $\infty$                  | 0               | $0^0$                                               | $180^{0}$                                      |

Table (2): Phase angle between  $V_0$  and  $V_i$

The total phase shift  $\theta_1$  between V<sub>0</sub> and V<sub>i</sub> is the sum of the phase shift of RC network and inherent phase shift (180<sup>0</sup>) introduced by the amplifier.

From table (2),

(i) The phase shift  $\theta_1$  due to RC network decreases from 90° to 0°. The plot of  $\theta_1$  V/s frequency is shown in Fig. (12).

(ii) The total phase  $\theta$ , decreases from 270° to 180°.

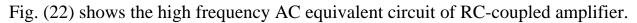

## Low frequency Response of BJT amplifier:

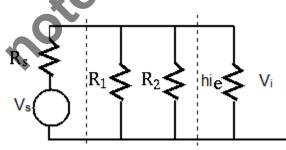

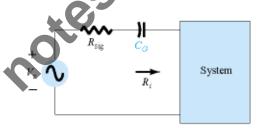

Fig. (13) shows the circuit of single stage BJT amplifier. The coupling capacitors  $C_s$  and  $C_c$  and bypass capacitor  $C_E$  determines the low frequency response.

## Effect of C<sub>s</sub> on low frequency response:

The input coupling capacitor  $C_S$  couples the source signal to BJT. First, we will neglect the effects of  $C_C$  and  $C_E$  i.e. they are treated as short circuits.

The AC equivalent circuit is obtained by reducing VCC to zero and  $C_C$  and  $C_E$  by their short circuit equivalent as shown in Fig. (14).

Fig. (13) Single stage BJT amplifier

Fig. (14) AC equivalent circuit

The resistance of the transistor between base-emitter is  $h_{ie}$ . The input AC equivalent circuit is shown in Fig. (15).

Fig. (15) Input AC equivalent

Let  $R_i = R_1 \| R_2 \| h_{ie} - \dots (18)$

Where  $h_{ie} = \beta r_e$ ----- (19)

Using voltage division rule in the circuit of Fig. (15) the voltage applied to the amplifier is

$$V_{i} = \frac{V_{S}R_{i}}{(R_{S}+R_{i})-fXc_{S}} - \dots (20)$$

Where

$$Xc_S = \frac{1}{2\pi f C_S}$$

----- (21)

$V_i = \frac{V_S \left[\frac{R_i}{R_S + R_i}\right]}{1 - j \left[\frac{X c_S}{R_i + R_S}\right]}$

$V_i = \frac{|V_{S|} \left[\frac{R_i}{R_S + R_i}\right]}{\sqrt{1 + j \left[\frac{X c_S}{R_i + R_S}\right]^2}}$  -----(22)

In the mid frequency band, f is large. As a result,  $Xc_S \rightarrow 0$ .

Therefore from Eq. (22),

$$|V_i|_{mid} = \frac{|V_S|R_i}{(R_{S+}R_i)}$$

----- (23)

$$|\mathbf{V}_{i}| = \frac{|\mathbf{V}i|\text{mid}}{\sqrt{1 + \left[\frac{Xc_{S}}{R_{i} + R_{S}}\right]^{2}}} \dots (24)$$

$|V_{i}|_{mid} = \frac{|V_{S}|R_{i}}{(R_{S}+R_{i})} - \dots (23)$ Therefore Eq. (22) becomes,  $|V_{i}| = \frac{|Vi|mid}{\sqrt{1 + \left[\frac{Xc_{S}}{R_{i}+R_{S}}\right]^{2}}} - \dots (24)$ The lower 3dB cut-off occurs when  $|V_{i}| = \frac{|Vi|mid}{\sqrt{2}} = 0.707 |V_{i}|_{mid}$

Therefore Eq. (24) becomes,

$$0.707 |V_i|_{\text{mid}} = \frac{|Vi|\text{mid}}{\sqrt{1 + \left[\frac{Xc_S}{R_i + R_S}\right]^2}}$$

This condition is satisfie, if  $\frac{Xc_S}{R_i + R_S} = 1$  or  $Xc_S = R_i + R_S$

$$\frac{1}{2\pi f C_S} = R_i + R_S$$

Therefore  $f = \frac{1}{2\pi (R_S + R_i)C_S}$  ----- (25)

Eq. (25) gives the lower 3dB cut-off frequency due to  $C_s$ .

Therefore

$$f_{Ls} = \frac{1}{2\pi (R_S + R_i)C_S}$$

----- (26)

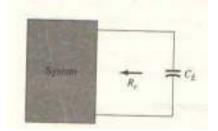

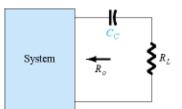

## Effect of output coupling capacitor C<sub>C</sub> on low frequency response :

The output coupling capacitor C<sub>C</sub> couples the output of the BJT to the load. The equivalent circuit on the output side by neglecting the effect of  $C_S$  and  $C_E$  by treating them as short circuits is as shown in Fig. (16).

.it Fig. (16) (a) AC equivalent circuit of output side (b) Simplified AC equivalent

Let

$$R_0 = r_0 || R_c ---- (27)$$

V<sub>C</sub>= output voltage of BJT

V<sub>0</sub>=load voltage

Using voltage division rule in circuit of Fig. (16) (a), the load voltage is,

$$V_{O} = \frac{V_{C}R_{L}}{(R_{O+}R_{L}) - jXc_{C}} - \dots - (28)$$

Where

$$Xc_C = \frac{1}{2\pi f C_C}$$

----- (29)

$$\mathbf{V}_{\mathrm{O}} = \frac{V_{C} \left[\frac{R_{L}}{R_{O} + R_{L}}\right]}{1 - j \left[\frac{X c_{C}}{R_{O} + R_{L}}\right]}$$

$$|V_{\rm O}| = \frac{|V_{C|} \left[\frac{R_L}{R_O + R_L}\right]}{\sqrt{1 + j \left[\frac{X c_C}{R_O + R_L}\right]^2}} \dots (30)$$

In the mid frequency band,  $Xc_c \rightarrow 0$

Therefore  $|V_0|_{mid} = \frac{|V_C|R_L}{(R_{O+}R_L)}$  ----- (31)

Substitute Eq. (31) in (30)

$$|V_{O}| = \frac{|Vo|mid}{\sqrt{1 + \left[\frac{Xc_{C}}{R_{O} + R_{L}}\right]^{2}}}$$

----- (32)

The lower 3dB cut-off occurs when  $|V_0| = \frac{|Vo|mid}{\sqrt{2}} = 0.707 |V_0|_{mid}$

This is possible iff,

$$\frac{Xc_C}{R_O + R_L} = 1 \text{ or } Xc_C = R_O + R_L$$

Therefore f=

$$\frac{1}{2\pi(R_O+R_L)C_C}$$

----- (33)

Eq. (33) gives the lower 3dB cut-off frequency due to  $C_c$ .

Therefore

$$f_{Lc} = \frac{1}{2\pi (R_O + R_L)C_C}$$

----- (34)

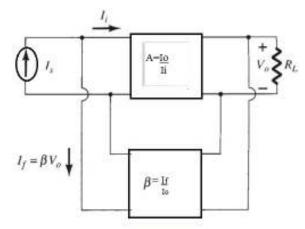

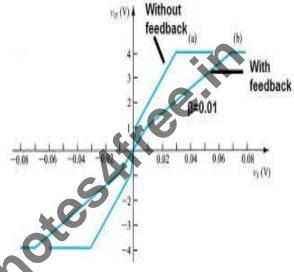

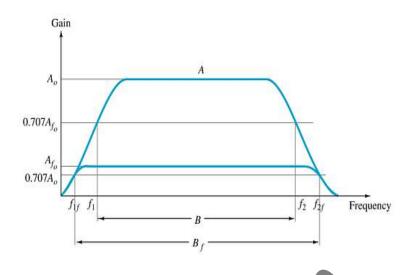

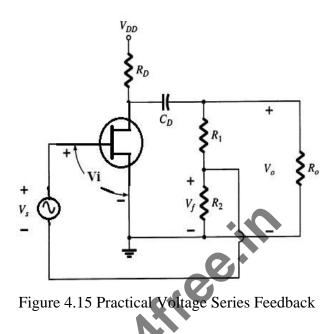

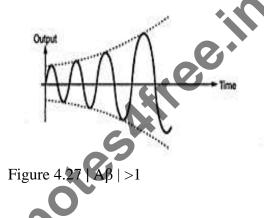

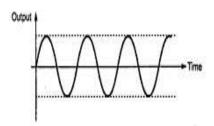

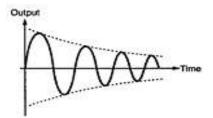

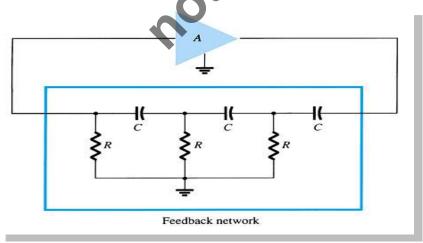

# Effect of Emitter bypass capacitor $C_E$ on low frequency response :